# **Application Note AN-1089**

# IRS2136xD and IR2136x Series Comparison

By Andrea Merello, David New

### Table of Contents

|                                                                          | Page   |

|--------------------------------------------------------------------------|--------|

| Introduction                                                             | 1      |

| Family Description and Definition                                        | 2      |

| Block Diagrams                                                           |        |

| Datasheet Changes                                                        |        |

| Absolute Maximum Ratings:                                                | 4      |

| Recommended Operating Conditions:                                        |        |

| Static Electrical Characteristics (Inputs Thresholds):                   |        |

| Table 4: IRS2136xD Inputs Thresholds                                     | 5      |

| Static Electrical Characteristics (Undervoltage Thresholds):             | 5      |

| Static Electrical Characteristics (V <sub>CC</sub> Supply Bias Current): | 5      |

| Static Electrical Characteristics (Input Clamps):                        | 6      |

| Static Electrical Characteristics (Inputs Leakage):                      | 6      |

| Dynamic Electrical Characteristics (Input Filters and Propagation Dela   | ays):6 |

| Dynamic Electrical Characteristics (Deadtime):                           | 8      |

| Dynamic Electrical Characteristics (TITRIP):                             | 9      |

| Conclusions                                                              |        |

|                                                                          |        |

#### Introduction

The IRS2136xD is a new family of products that can replace the IR2136x family advantageously by providing functionality improvements, some of which will results in system-level cost savings (e.g., integration of the bootstrap network). These two families are based on the same core design and are pin-to-pin compatible, allowing minimal changes to the previous design. This application note describes the various differences between the existing IR2136x IC family and the new IRS2136xD family, and provides helpful information for adopting the new IRS2136xD HVICs into existing designs.

# Family Description and Definition

The IRS213(6, 62, 63, 65, 66, 67, 68) HVICs are high voltage, high speed power MOSFET and IGBT drivers with three independent high and low side referenced output channels for 3-phase applications.

Proprietary HVIC technology enables rugged monolithic construction. Logic inputs are compatible with CMOS or LSTTL outputs, down to 3.3 V logic. A current trip function which terminates all six outputs can be derived from an external current sense resistor. An enable function is available to terminate all six outputs simultaneously. An open-drain FAULT signal is provided to indicate that an over-current or undervoltage shutdown has occurred.

Over-current fault conditions are cleared automatically after a delay (which is programmed externally via an RC network connected to the RCIN input). The output drivers feature a high pulse current buffer stage designed for minimum driver cross-conduction. Propagation delays are matched to simplify use in high frequency applications. The floating channel can be used to drive N-channel power MOSFETs or IGBTs in the high side configuration which operates up to 600 V.

The new IRS2136xD family introduces some parameter changes. In particular this family features a high voltage bootstrap FET that enables the use of these gate drivers without the external bootstrap network to supply the floating gate driver sections. Table 1 summarizes the main characteristics of the members of IRS2136xD family. A detailed parameter description/comparison of the two families follows after a block diagram comparison.

| Part                                       | IRS2136D                                       | IRS21362D  | IRS21363D                                      | IRS21365D                                      | IRS21366D                                      | IRS21367D                                      | IRS21368D                                      |

|--------------------------------------------|------------------------------------------------|------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|

| Input<br>Logic                             | $\overline{\text{HIN}}, \overline{\text{LIN}}$ | HIN, LIN   | $\overline{\text{HIN}}, \overline{\text{LIN}}$ |

| t <sub>on</sub> (typ.)                     | 530 ns (1)                                     | 530 ns (1) | 530 ns (1)                                     | 530 ns (1)                                     | 200 ns                                         | 200 ns                                         | 530 ns (1)                                     |

| t <sub>off</sub> (typ.)                    | 530 ns (1)                                     | 530 ns (1) | 530 ns (1)                                     | 530 ns (1)                                     | 200 ns                                         | 200 ns                                         | 530 ns (1)                                     |

| V <sub>IH</sub> (min.)                     | 2.5 V                                          | 2.5 V      | 2.5 V                                          | 2.5 V                                          | 2.5 V                                          | 2.5 V                                          | 2.5 V                                          |

| V <sub>IL</sub> (max.)                     | 0.8 V                                          | 0.8 V      | 0.8 V                                          | 0.8 V                                          | 0.8 V                                          | 0.8 V                                          | 0.8 V                                          |

| V <sub>ITRIP+</sub>                        | 0.46 V                                         | 0.46 V     | 0.46 V                                         | 4.3 V                                          | 0.46 V                                         | 4.3 V                                          | 4.3 V                                          |

| V <sub>CCUV+</sub> /<br>V <sub>BSUV+</sub> | 8.9 V                                          | 10.4 V     | 11.1 V                                         | 11.1 V                                         | 11.1 V                                         | 11.1 V                                         | 8.9 V                                          |

| V <sub>CCUV-</sub> /<br>V <sub>BSUV-</sub> | 8.2 V                                          | 9.4 V      | 10.9 V                                         | 10.9 V                                         | 10.9 V                                         | 10.9 V                                         | 8.2 V                                          |

(1) Features a redesigned input filter. Please see page 6 for details.

Table 1: IRS2136xD Summary Table

# **Block Diagrams**

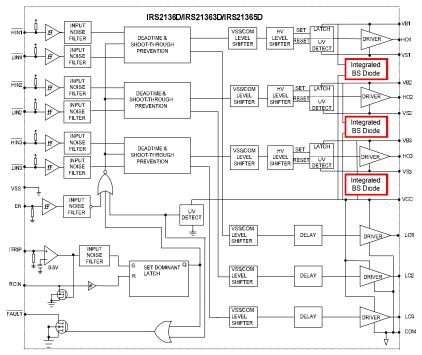

The IR2136, IR21363 and IR21365 share the same block diagram (presented on page 6 of the IR2136x datasheet available at <u>www.irf.com</u>). The IRS2136D, IRS21363D and IRS21365D block diagram is shown in Fig. 1. The only visible difference is represented by the "Integrated BS Diode" block that applies to all new versions.

Figure 1: IRS2136D, IRS21363D, IRS21365D Block Diagram

The same considerations apply for the other block diagrams of the two families with one exception. Both the IR21368 and IRS21368D do have the "input filter" block after the HIN/LIN Schmitt triggers as shown in the IRS21368D datasheet on page 13.

The IRS2136xD datasheet addresses the internal bootstrap FET working principle and is documented in the application section. Its equivalent series resistance is mentioned the "Static Electrical Characteristics" section and is reproduced here is Table 2.

| Symbol          | Definition                        | Min | Тур | Max | Units |

|-----------------|-----------------------------------|-----|-----|-----|-------|

| R <sub>BS</sub> | Internal BS diode R <sub>ON</sub> | -   | 200 | _   | Ω     |

|                 | Table 2: D. Cresting              |     |     |     |       |

Table 2: R<sub>BS</sub> Specification

The integrated bootstrap MOSFET is turned on only during the time when LO is 'high', and has a limited source current due to  $R_{BS}$ . The VBS voltage will be charged each cycle depending on the on-time of LO and the value of the CBS capacitor, the DS/CE drop of the external MOSFET/IGBT or the low side free-wheeling diode drop.

In sinusoidal or space vector modulated configurations, the integrated bootstrap diode can replace the external bootstrap network. Limitations may apply for long periods of PWM duty cycle close to 100%. Six step based control schemes still need an external bootstrap diode and resistor to function properly.

### **Datasheet Changes**

#### Absolute Maximum Ratings:

The absolute maximum ratings for  $V_B-V_S$ ,  $V_{cc}$ -COM,  $V_{cc}-V_{ss}$ , LO-COM and HO- $V_s$  of the IRS2136xD family are shown in Table 3. The maximum allowable DC supply has changed from 25 V to 20 V for  $V_{CC}$  to  $V_{SS}$  and for  $V_B$  to  $V_S$ , while  $V_{CC}$  to COM remains 25 V. The recommended operating voltage of the two families remains the same (20 V). The IRS2136xD series embeds a clamp structure on the supply pins capable of cutting fast and low-power spikes that may be dangerous for the IC.

#### **Recommended Operating Conditions:**

The recommended operating conditions of the two families have remained unchanged. Note 1 on page 2 of the IR2136xD datasheet has been changed in the IRS2136xD datasheet. The IRS2136xD Note 1 shows an important improvement of DC operation under negative Vs condition.

**IR2136x Note 1:** Logic operational for V<sub>S</sub> of COM -5 V to COM +600 V. Logic state held for V<sub>S</sub> of COM -5 V to COM – V<sub>BS.</sub>

**IRS2136xD Note 1:** Logic operational for V<sub>S</sub> of COM-8 V to COM +600 V. Logic state held for V<sub>S</sub> of COM-8 V to COM – V<sub>BS.</sub>

| Symbol          | Definition                              | Min.                                   | Max.                       | Units |

|-----------------|-----------------------------------------|----------------------------------------|----------------------------|-------|

| Vs              | High side offset voltage                | V <sub>B 1,2,3</sub> - <mark>20</mark> | V <sub>B 1,2,3</sub> + 0.3 |       |

| VB              | High side floating supply voltage       | -0.3                                   | 625                        | V     |

| V <sub>cc</sub> | Low side and logic fixed supply voltage | -0.3                                   | 25                         | v     |

| V <sub>SS</sub> | Logic ground                            | V <sub>cc</sub> - <mark>20</mark>      | V <sub>CC</sub> + 0.3      |       |

Table 3: IRS2136xD Absolute Maximum Extraction

# International

#### Static Electrical Characteristics (Inputs Thresholds):

The input thresholds shown in Table 4 have been added to the new IRS2136xD datasheet. Input thresholds refer to HIN and LIN inputs.

Additionally, the IRS2136xD family features improved logic threshold values for higher signal to noise rejection at the inputs. Previously, most of the IR2136x HVICs were specified as  $V_{IH} = 3.0$  V; all of the IRS2136xD HVICs are specified as  $V_{IH} = 2.5$  V.

| Symbol                           | Definition                                                                                                                                | Min              | Тур | Max | Units |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----|-----|-------|

| VIH                              | Logic "0" input voltage LIN1,2,3 / HIN1,2,3<br>IRS213(6, 63, 65, 66, 67, 68)D<br>Logic "1" input voltage LIN1,2,3 / HIN1,2,3<br>IRS21362D | <mark>2.5</mark> | _   | _   | V     |

| V <sub>IN</sub> , <sub>TH+</sub> | Input positive going threshold                                                                                                            | —                | 1.9 | —   |       |

| $V_{IN,TH-}$                     | Input negative going threshold                                                                                                            | _                | 1   | _   |       |

Table 4: IRS2136xD Inputs Thresholds

#### Static Electrical Characteristics (Undervoltage Thresholds):

The new design introduced a small variation in the undervoltage thresholds for three of the IRS213(63, 65, 66, 67)D parts. The variations are small (a decrease of 0.2 V for the minimum specifications) and likely will not cause any issues for most applications; Table 5 shows the IRS213(63, 65, 66, 67)D values.

| Symbol                                  | Definition                                                   | Min               | Тур  | Max  | Units |

|-----------------------------------------|--------------------------------------------------------------|-------------------|------|------|-------|

| V <sub>CCUV+</sub> / V <sub>BSUV+</sub> | V <sub>CC</sub> supply undervoltage positive going threshold | <mark>10.4</mark> | 11.1 | 11.6 | V     |

| V <sub>CCUV-</sub> / V <sub>BSUV-</sub> | V <sub>CC</sub> supply undervoltage positive going threshold | <mark>10.2</mark> | 10.9 | 11.4 | V     |

Table 5: UVLO Thresholds for IRS213(63, 65, 66, 67)D

#### Static Electrical Characteristics (V<sub>CC</sub> Supply Bias Current):

The integrated bootstrap feature requires additional bias current; current consumption has increased as shown in Tables 6 and 7. The small increase of current should not cause difficulties for most applications.

| Symbol                                     | Definition                               | Min | Тур              | Max              | Units | Symbol                        |

|--------------------------------------------|------------------------------------------|-----|------------------|------------------|-------|-------------------------------|

| I <sub>QCC</sub>                           | Quiescent V <sub>CC</sub> supply current | _   | <mark>1.6</mark> | <mark>2.3</mark> | mA    | all inputs @<br>logic 0 value |

| <br>Table 6: IR2136x Var Quiescent Current |                                          |     |                  |                  |       |                               |

Table 6: IR2136x V<sub>CC</sub> Quiescent Current

| Symbol           | Definition                               | Min        | Тур            | Max            | Units | Symbol                        |

|------------------|------------------------------------------|------------|----------------|----------------|-------|-------------------------------|

| I <sub>QCC</sub> | Quiescent V <sub>CC</sub> supply current | _          | <mark>3</mark> | <mark>4</mark> | mA    | all inputs @<br>logic 0 value |

|                  | Table 7, IDS2126, DV Outered             | at Currant |                |                |       |                               |

Table 7: IRS2136xD Vcc Quiescent Current

#### Static Electrical Characteristics (Input Clamps):

The input clamp specifications of the two families are compared in Tables 8 and 9. When a current limiting resistor is already present in the application, this higher variation in the clamp voltage will not affect the inverter design.

| Symbol                | Definition                                   | Min              | Тур | Max              | Units | Symbol                  |  |  |

|-----------------------|----------------------------------------------|------------------|-----|------------------|-------|-------------------------|--|--|

| V <sub>IN,CLAMP</sub> | Input clamp voltage (HIN, LIN, ITRIP and EN) | <mark>4.9</mark> | 5.2 | <mark>5.5</mark> | V     | I <sub>IN</sub> =100 μΑ |  |  |

|                       | Table 8: Input Clamp Voltage IR2136x         |                  |     |                  |       |                         |  |  |

| Symbol                                | Definition                                   | Min              | Тур | Max               | Units | Symbol                  |

|---------------------------------------|----------------------------------------------|------------------|-----|-------------------|-------|-------------------------|

| V <sub>IN,CLAMP</sub>                 | Input clamp voltage (HIN, LIN, ITRIP and EN) | <mark>4.8</mark> | 5.2 | <mark>5.65</mark> | V     | I <sub>IN</sub> =100 μA |

| Table 9: Input Clamp Voltage IRS2136x |                                              |                  |     |                   |       |                         |

Table 9: Input Clamp Voltage IRS2136x

#### Static Electrical Characteristics (Inputs Leakage):

In order to measure the leakage current due only to the pull-up or pull-down resistors connected to the input pins and keep the input clamp inactive during such a test, the V<sub>in</sub> test condition has been changed from 5 V to 4 V. For this reason, the IRS2136xD current absorption is reduced when compared to the IR2136x family.

#### **Dynamic Electrical Characteristics (Input Filters and Propagation Delays):**

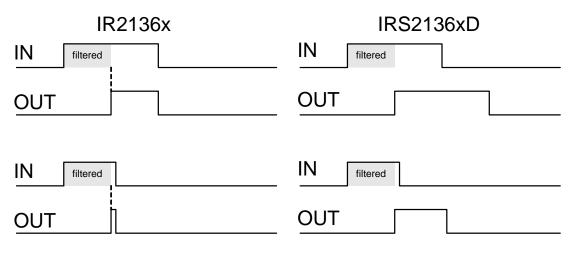

One of the major changes introduced by the new IRS2136xD HVIC family is the redesigned input filters. The new input filters provide lower pulse distortion and better spike noise rejection as well as short pulses rejection. The input filters have been applied to the HIN and LIN inputs as well as the EN (enable) pin. The working principle of new filters is shown in Fig. 2.

# International

Figure 2: Input Filters Comparison

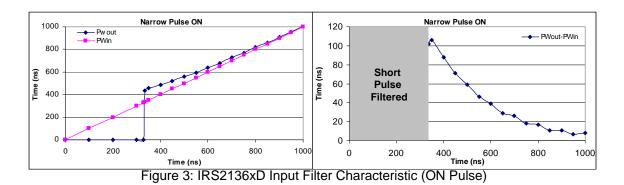

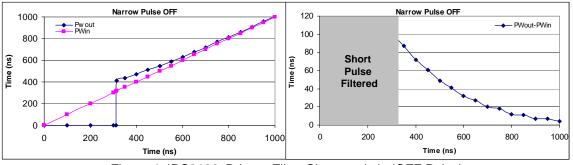

The input filter characteristics are shown in Figs. 3 and 4 for narrow on (short positive pulse) and narrow off pulses (short negative pulse). The new IRS2136xD input filter is the cause of the increased propagation delays (i.e.,  $t_{on}$  and  $t_{off}$ ).

Figure 4: IRS2136xD Input Filter Characteristic (OFF Pulse)

# International **ICR** Rectifier

It should be noticed that with the IRS2136xD family, the  $t_{on}$  and  $t_{off}$  propagation delays are equal, allowing very low pulse width distortion for long pulses. Additionally, matching delay time decreased 50 ns max. Tables 10 and 11 show the propagation delay differences specified in the IR2136x and IRS2136xD datasheets. For the gate drivers which do not have input filters (i.e., IRS21366D and IRS21367D), the propagation delay times ( $t_{on}$  and  $t_{off}$ ) have been reduced and allow lower pulse width distortion.

The minimum HIN pulse width has changed from 1  $\mu$ s to 500 ns (as shown in the following note) to allow higher PWM control. This change in the specification may affect applications where the controller takes actions related to propagation delays.

#### IR2136x Note: For high side PWM, HIN pulse width must be ≥ 1000 ns

| Symbol                    | Definition                                                        | Min              | Тур              | Мах              | Units | Test Conditions                            |

|---------------------------|-------------------------------------------------------------------|------------------|------------------|------------------|-------|--------------------------------------------|

| t <sub>on</sub>           | Turn-on propagation delay                                         | <mark>300</mark> | <mark>425</mark> | <mark>550</mark> |       |                                            |

| t <sub>off</sub>          | Turn-off propagation delay                                        | <mark>250</mark> | <mark>400</mark> | <mark>550</mark> |       | V <sub>IN</sub> = 0 V & 5 V                |

| t <sub>on</sub> (66, 67)  | Turn-on propagation delay                                         | —                | <mark>250</mark> | _                |       | $v_{\rm IN} = 0$ v $\alpha$ 5 v            |

| t <sub>off</sub> (66, 67) | Turn-off propagation delay                                        | _                | <mark>180</mark> | _                |       |                                            |

| t <sub>EN</sub>           | ENABLE low to output shutdown propagation delay                   | <mark>300</mark> | <mark>450</mark> | <mark>600</mark> | ns    | $V_{\text{IN},}V_{\text{EN}}$ = 0 V or 5 V |

| t <sub>EN</sub> (66, 67)  | ENABLE low to output shutdown propagation delay                   | 100              | <mark>250</mark> | 400              |       | $V_{IN,} V_{EN} = 0 V$ or 5 V              |

| t <sub>FILIN</sub>        | Input filter time (HIN, LIN)<br>(IRS213(6, 62, 63, 65, 68)D only) | 100              | <mark>200</mark> | _                |       | $V_{IN} = 0 \ V \ \& \ 5 \ V$              |

| MT                        | t <sub>on</sub> , t <sub>off</sub> matching time                  | _                | 40               | <mark>75</mark>  |       | Ext. deadtime<br>>400 ns                   |

IRS2136xD Note: For high side PWM, HIN pulse width must be ≥ 500 ns

Table 10: Propagation and Filter Timing (IR2136x)

| Symbol                   | Definition                                                        | Min              | Тур              | Max              | Units | Test Conditions                            |

|--------------------------|-------------------------------------------------------------------|------------------|------------------|------------------|-------|--------------------------------------------|

| t <sub>on</sub>          | Turn-on propagation delay                                         | <mark>400</mark> | <mark>530</mark> | <mark>750</mark> |       |                                            |

| t <sub>off</sub>         | Turn-off propagation delay                                        | <mark>400</mark> | <mark>530</mark> | <mark>750</mark> |       | V <sub>IN</sub> = 0 V & 5 V                |

| t <sub>on</sub> (66,67)  | Turn-on propagation delay                                         | _                | <mark>200</mark> | _                |       |                                            |

| t <sub>off</sub> (66,67) | Turn-off propagation delay                                        | _                | <mark>200</mark> | _                |       |                                            |

| t <sub>EN</sub>          | ENABLE low to output shutdown propagation delay                   | <mark>350</mark> | <mark>460</mark> | <mark>650</mark> | ns    | $V_{\text{IN},}V_{\text{EN}}$ = 0 V or 5 V |

| t <sub>EN</sub> (66, 67) | ENABLE low to output shutdown propagation delay                   | _                | <mark>300</mark> | _                |       | $V_{IN,} V_{EN} = 0 V$ or 5 V              |

| t <sub>FILIN</sub>       | Input filter time (HIN, LIN)<br>(IRS213(6, 62, 63, 65, 68)D only) | <mark>200</mark> | <mark>350</mark> | <mark>510</mark> |       | V <sub>IN</sub> = 0 V & 5 V                |

| МТ                       | $t_{on}$ , $t_{off}$ matching time (on all six channels)          | —                | _                | <mark>50</mark>  |       | Ext. deadtime<br>>420 ns                   |

Table 11: Propagation and Filter Timing (IRS2136xD)

#### Dynamic Electrical Characteristics (Deadtime):

Deadtime tolerances have increased. The min/max values add additional margins and should not cause problems to existing designs. Deadtime matching

has improved from 70 ns to 60 ns for the new family; this change should not negatively affect existing designs. Tables 12 and 13 provide a comparison.

#### **Dynamic Electrical Characteristics (T<sub>ITRIP</sub>):**

The ITRIP blanking time (T<sub>ITRIP</sub>) has increased to increase over-current detection reliability and to reduce the need of an external noise filters at the ITRIP pin. The overall propagation delay (max) for both shutdown and fault communication has increased slightly. No changes will be needed in applications already using the IR2136x family. Tables 14 and 15 provide a comparison.

| Symbol | Definition                                    | Min              | Тур | Max              | Units | Test<br>Conditions          |

|--------|-----------------------------------------------|------------------|-----|------------------|-------|-----------------------------|

| DT     | Deadtime                                      | <mark>220</mark> | 290 | <mark>360</mark> | ns    | $V_{IN} = 0 \ V \ \& 5 \ V$ |

| MDT    | DT matching (Hi->Lo & Lo->Hi on all channels) | _                | 25  | <mark>70</mark>  | ns    | Ext. deadtime<br>>400 ns    |

| Symbol | Definition                                    | Min              | Тур | Max              | Units | Test Conditions                             |

|--------|-----------------------------------------------|------------------|-----|------------------|-------|---------------------------------------------|

| DT     | Deadtime                                      | <mark>190</mark> | 290 | <mark>420</mark> | ns    | $V_{IN} = 0 V \& 5 V$<br>ext. deadtime >0 s |

| MDT    | DT matching (Hi->Lo & Lo->Hi on all channels) | —                | _   | <mark>60</mark>  | ns    | Ext. deadtime >0 s                          |

Table 12: Deadtime IR2136x

#### Table 13: Deadtime IRS2136xD

| tITRIP to FAULT propagation delay400600800 $V_{IN} = 0 \text{ V or }$ tITRIP blacking time100150 | Symbol             | Definition                                 | Min | Тур              | Max               | Units | <b>Test Conditions</b>                           |

|--------------------------------------------------------------------------------------------------|--------------------|--------------------------------------------|-----|------------------|-------------------|-------|--------------------------------------------------|

| $t_{FLT}$ ITRIP to FAOL 1 propagation delay     400     600     800 $V_{ITRIP} = 5^{-1}$ t_t     | t <sub>ITRIP</sub> | ITRIP to output shutdown propagation delay | 500 | 750              | <mark>1000</mark> |       | $V_{\text{ITRIP}} = 5 \text{ V}$                 |

|                                                                                                  | t <sub>FLT</sub>   | ITRIP to FAULT propagation delay           | 400 | 600              | <mark>800</mark>  |       | $V_{IN} = 0 V \text{ or } 5 V$ $V_{ITRIP} = 5 V$ |

|                                                                                                  | t <sub>bl</sub>    | ITRIP blanking time                        | 100 | <mark>150</mark> | _                 | ns    | $V_{IN} = 0 V \text{ or } 5 V$ $V_{ITRIP} = 0 V$ |

Table 14: Over-current Trip Related Parameters (IR2136x)

| Symbol             | Definition                                 | Min | Тур              | Max               | Units | <b>Test Conditions</b>                              |

|--------------------|--------------------------------------------|-----|------------------|-------------------|-------|-----------------------------------------------------|

| t <sub>ITRIP</sub> | ITRIP to output shutdown propagation delay | 500 | 750              | <mark>1200</mark> |       | V <sub>ITRIP</sub> = 5 V                            |

| t <sub>FLT</sub>   | ITRIP to FAULT propagation delay           | 400 | 600              | <mark>950</mark>  |       | $V_{IN} = 0 V \text{ or } 5 V$<br>$V_{ITRIP} = 5 V$ |

| t <sub>bl</sub>    | ITRIP blanking time                        | _   | <mark>500</mark> | _                 | ns    | $V_{IN} = 0 V \text{ or } 5 V$<br>$V_{ITRIP} = 5 V$ |

Table 15: Over-current Trip Related Parameters (IRS2136xD)

# Conclusions

In most cases, any member of the IR2136x family will be easily and advantageously replaced by the new lead-free IRS2136xD family. The application will benefit from a monolithic solution which has an integrating the bootstrap circuit and features improved input filters.

http://www.irf.com Data and specifications subject to change without notice. 05/21/06