|

International Rectifier’s SureCHIP Program is a process regimen that combines

high-volume manufacturing and assembly with precision parametric testing and

special packaging to deliver Known Good Die (KGD) power semiconductors. The

KGD process provides measurably higher yields and is an economically viable

solution in the manufacturing of multi-chip modules (MCMs). As part of the

SureCHIP process, individual good die from probed and sawn wafers are transferred

to a custom-designed test nest for 100% electrical and visual testing.

SureCHIP power semiconductor die are packaged into tape and reel in a nitrogen

atmosphere or into chip trays for shipment. The SureCHIP KGD process is

qualified for 100% DC parametric testing. Additionally, avalanche testing on

MOSFETs and short circuit testing on IGBTs can be performed.

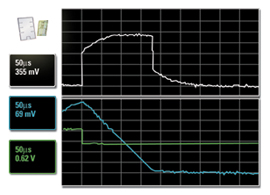

Sample Avalanche Test Results

|

|

THE IR ADVANTAGE

|