**Class D Amplifier Design Basics II**

02/19/2009 Rev 1.0

International **TOR** Rectifier

# Contents

**Chapter 1** Getting Familiar with Class D Audio Amplifier

Chapter 2 Latest Class D Audio Amplifier Technology Trend

**Chapter 3** Identifying Problems ~ Performance Measurement of Class D Amplifier

Chapter 4 Reducing Distortion ~Dead-time ~ LPF Designs

**Chapter 5** Reducing Noise ~ Isolation Technique ~ PCB Design

**APPENDIX** Simulation of a Simple Class D Amplifier

# Chapter 1: Getting Familiar with Class D Audio Amplifier

**IGR** International Rectifier

V<sub>OUT</sub> = B (2D-1)

In concept, Class D amplifier is linear; i.e. 0% distortion.

IOR International Rectifier

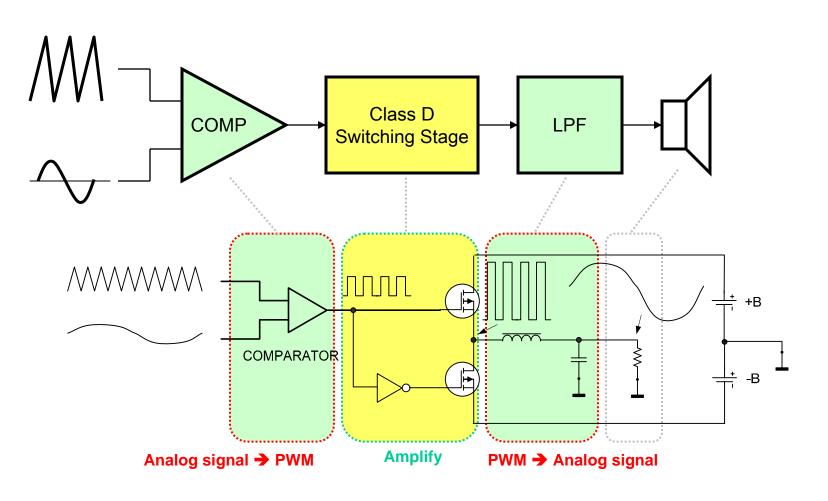

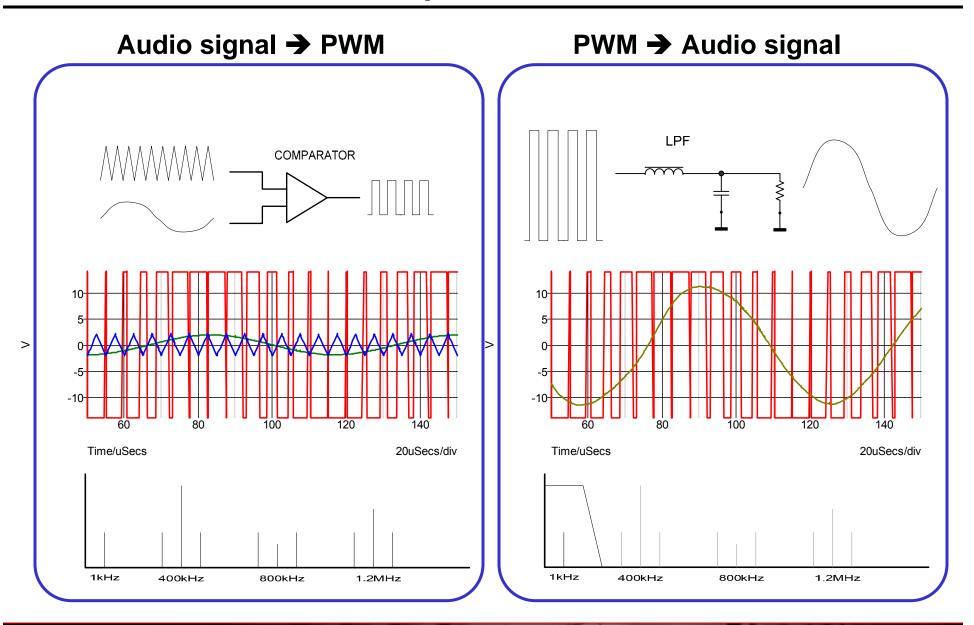

# **PWM: Heart of Class D Operation**

#### **ICR** International Rectifier

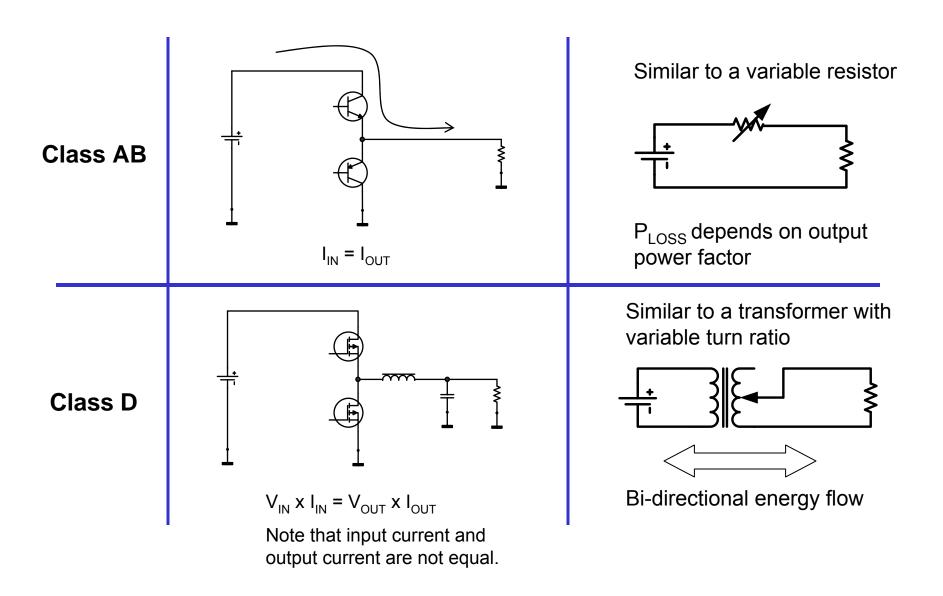

| Feature     | Class D Advantage                                                                                 | Class AB                        |

|-------------|---------------------------------------------------------------------------------------------------|---------------------------------|

| Efficiency  | Superior efficiency                                                                               |                                 |

|             | Efficiency can be improved with device technology                                                 | Efficiency is fixed.            |

|             | Suitable to drive lower impedance load                                                            | Extremely inefficient when      |

|             |                                                                                                   | driving lower impedance load.   |

|             | Can drive reactive load without significant degradation of                                        | Extremely inefficient when      |

|             | efficiency                                                                                        | driving reactive load.          |

|             | Requires smaller power supply                                                                     |                                 |

| Energy flow | Bi-directional energy flow; any energy reflected from the                                         | All the reflected energy from   |

|             | load is recycled to the power supply. Suitable to drive                                           | reactive components and back    |

|             | highly reactive load, such as woofer, speaker system                                              | EMF are consumed dissipating    |

|             | with dividing network, piezo speaker, etc.                                                        | heat                            |

| Drivability |                                                                                                   | The output device has high      |

|             | Inherently has low output impedance (m ohm range)                                                 | impedance, ~tens of k ohm.      |

|             |                                                                                                   | With a strong voltage feedback, |

|             |                                                                                                   | Class AB can achieve low        |

|             |                                                                                                   | output impedance.               |

|             |                                                                                                   | Power supply current = load     |

|             | Lower impedance loading does not burden power supply.<br>(Power supply current) ≠ (load current). | current. For a given output     |

|             |                                                                                                   | power with decreased load       |

|             |                                                                                                   | impedance, the supply current   |

|             |                                                                                                   | and heat dissipation in the     |

|             |                                                                                                   | output device increase.         |

|             | Wide power bandwidth; no extra effort to drive high                                               | Cross conduction limits high    |

|             | frequency rated power.                                                                            | frequency power bandwidth.      |

| Feature        | Class D Advantage                                                                                               | Class AB                                                                                                                                             |

|----------------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Linearity      | Topology is inherently linear without feedback                                                                  | Output device is non-linear;<br>exponential in BJT, quadratic in<br>MOSFET. Strong feedback is<br>necessary to achieve good<br>linearity.            |

|                | Cross over distortion is not in zero crossing area                                                              | Cross over distortion is at where<br>load current crosses zero,<br>which is most critical point of<br>operation.                                     |

| Stability      | Thermally stable; gain of the Class D stage, bandwidth, loop-gain are independent of output device temperature. | Output devices in linear<br>operating mode has strong<br>temperature coefficient in gain.<br>Loop-gain is changing<br>dynamically with output power. |

|                | No bias-current thermal compensation                                                                            |                                                                                                                                                      |

| Noise immunity | Inherently immune to incoming noise; low drive impedance, inductor between the load and amplifier.              | Because of strong non-linearity<br>in device and 'exposed'<br>feedback node, weak to RF<br>noise.                                                    |

| Reliability    | Higher reliability from less heat. Less metal fatigue in solder joints.                                         |                                                                                                                                                      |

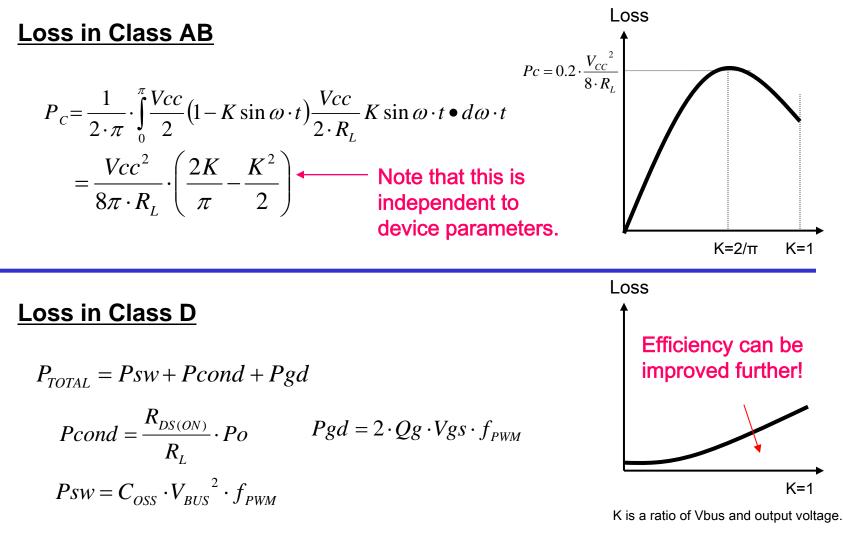

To learn more about power losses in Class D, refer to AN-1070 Class D Amplifier Performance Relationship to MOSFET Parameters.

**ICR** International Rectifier

# **MOSFET Basics**

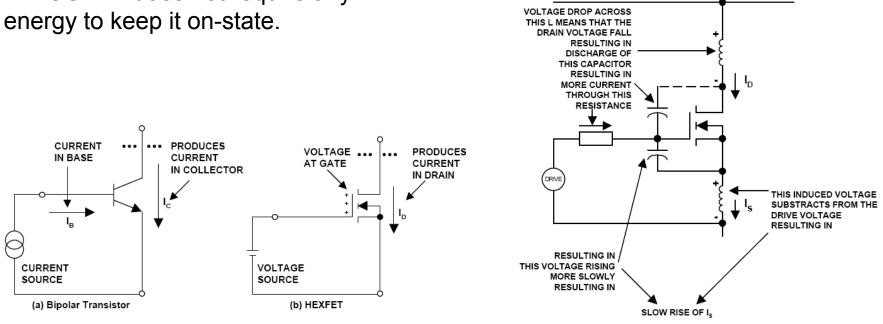

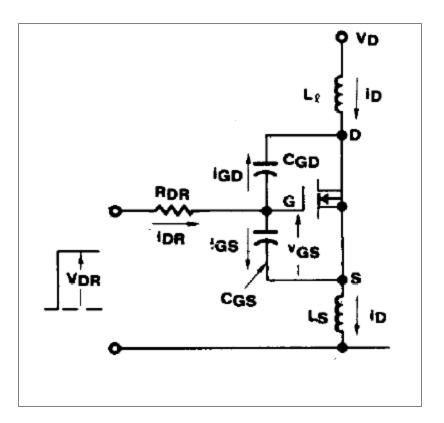

A MOSFET is a device to switch electronic current. A driving MOSFET charges/discharges a capacitor (Gate to Source, Gate to Drain).

A MOSFET does not require any

In switching transition, stray impedance in each terminal slows down switching and generates unwanted rings.

To learn more about power MOSFETs, refer to AN-1084 Power MOSFET Basics.

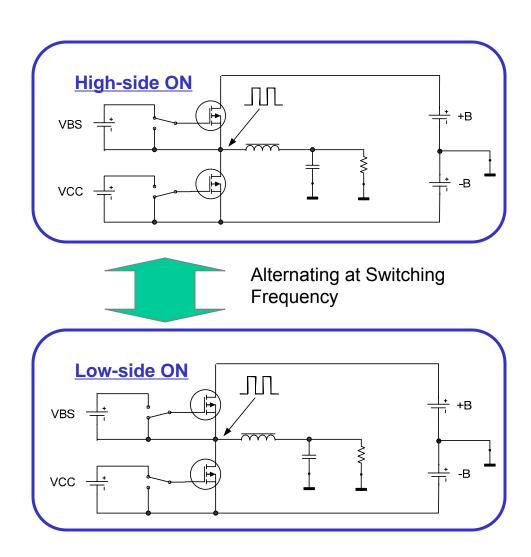

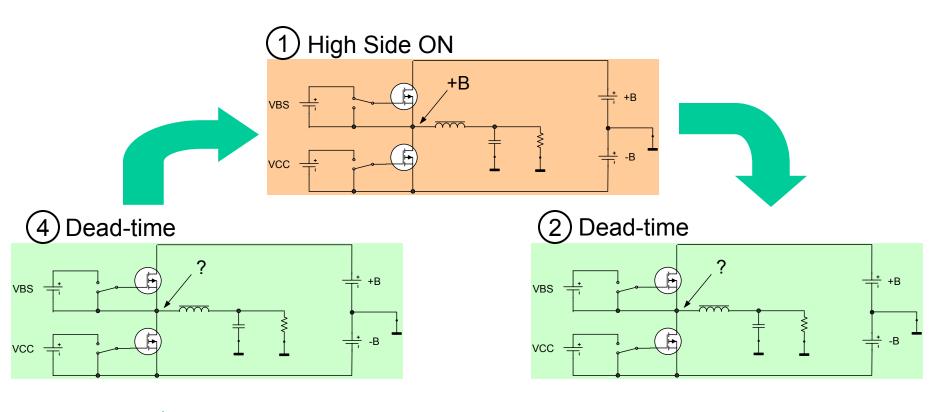

- Only one side, either high-side or lowside, MOSFET is ON at a time.

- The ratio of ON time between the highside and low-side MOSFETs determines the output voltage.

#### Driving a high-side MOSFET

- A floating power supply that referenced to switching node drives the gate of the high-side MOSFET

- The floating power supply is charged when the low-side MOSFET is ON. (Bootstrap power supply)

#### Driving a low-side MOSFET

• A bias voltage that refers to negative bus voltage –B drives the gate of the low-side MOSFET.

NOTE: In a practical design, a dead-time where both high- and low-side MOSFETs are off is inserted to prevent simultaneous ON state. Refer to chapter 4 for more details.

#### **IGR** International Rectifier

# **Bootstrap High Side Power Supply**

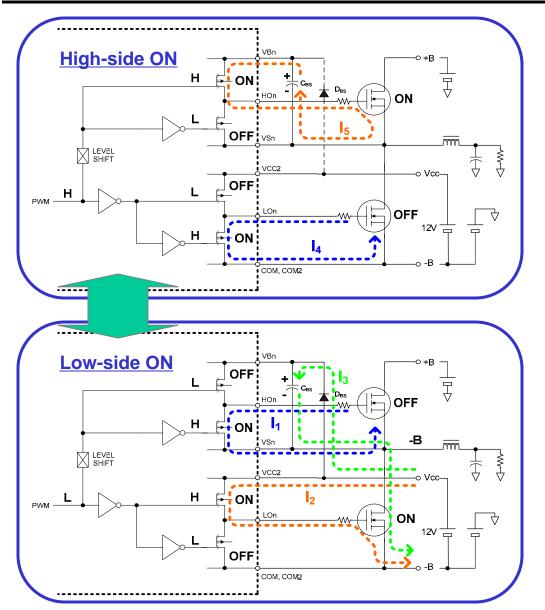

- $I_4$  turns off the low-side MOSFET. Then,  $I_5$  turns on the high-side MOSFET, lifting VS up to +B. As long as the high side is ON, bootstrap diode  $D_{BS}$  isolates the floating power supply VBS and bootstrap capacitor  $C_{BS}$  retains  $V_{BS}$ voltage.

- After the high-side MOSFET ON state,  $I_1$  turns off the high-side MOSFET, then  $I_2$  turns on the low side MOSFET. As soon as switching node VS reaches negative supply –B, the bootstrap diode  $D_{BS}$  turns on and starts charging bootstrap capacitor  $C_{BS}$  with current  $I_3$  from  $V_{CC}$ .

- Note that  $V_{BS} = V_{CC}$  (forward drop voltage of  $D_{BS}$ ).

#### ICR International Rectifier

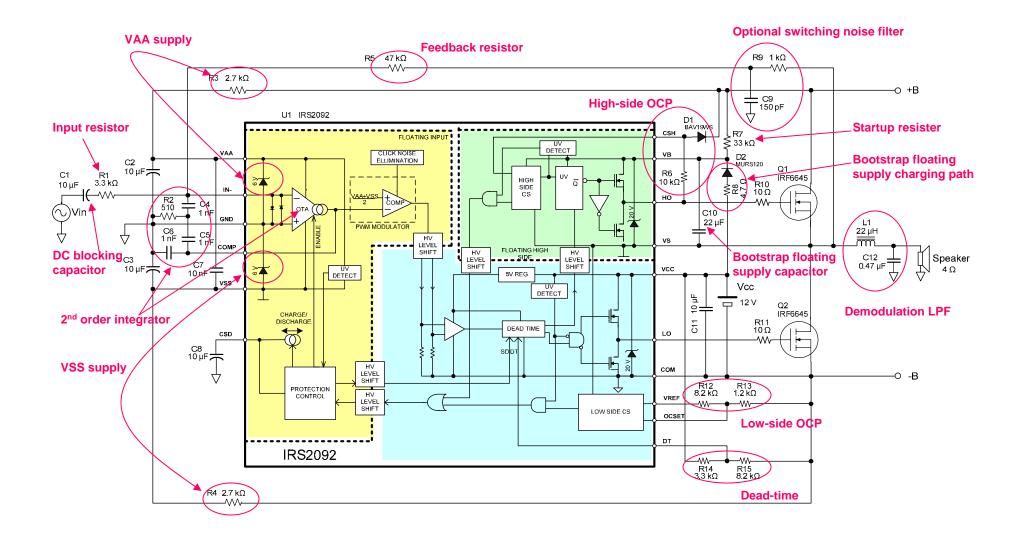

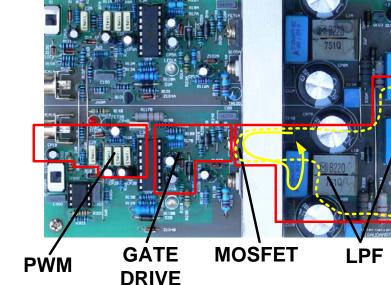

## **Example of a 100W Class D Amplifier**

.

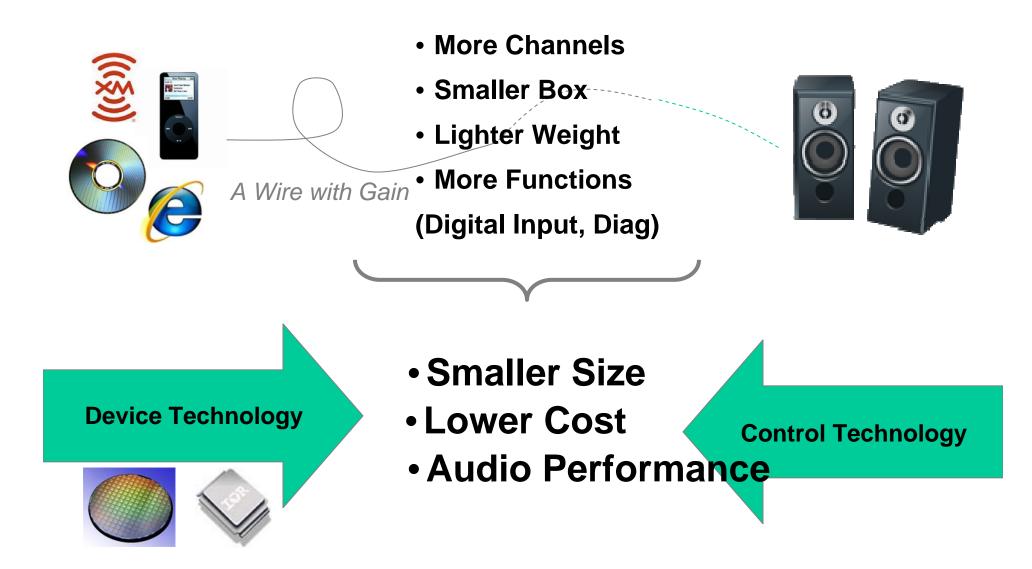

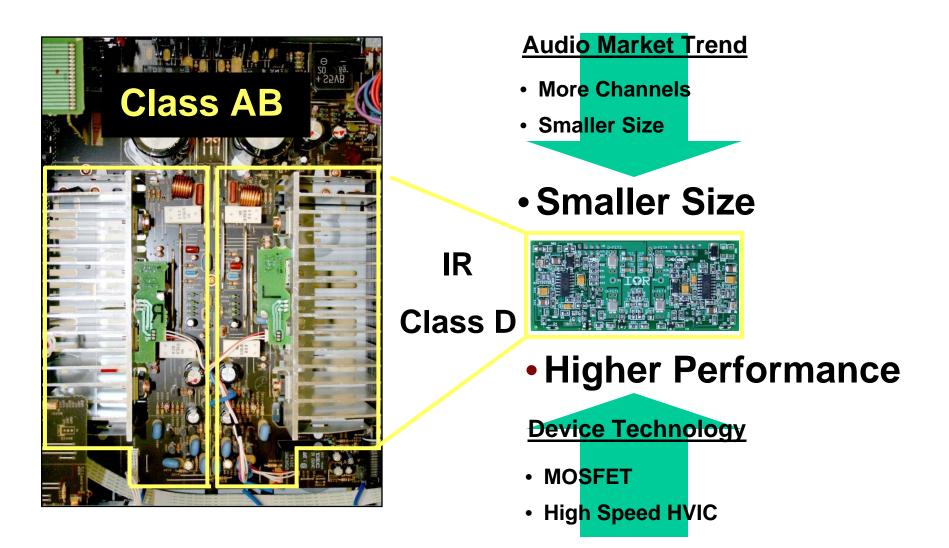

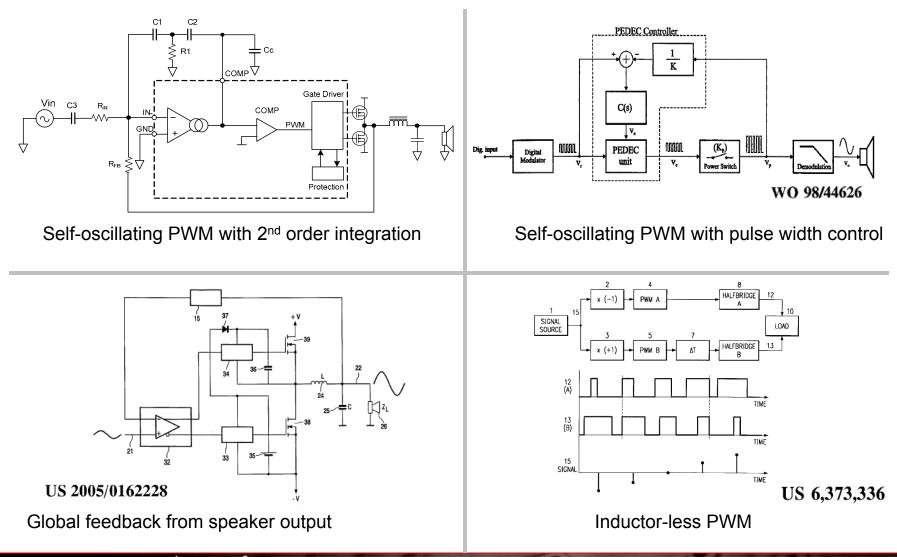

# Chapter 2: Latest Class D Audio Amplifier Technology Trend

**Device Technologies**

Packaging Technology

Signal Processing Technologies

- MOSFET FOM (Figure of Merit) improvements

- Higher voltage capability

- Faster and accurate switching time

- High gain low noise

process

- High GBW (Gain Band-Width) process

- Smaller

- Low stray inductance

- Surface mount

- Dual sided cooling

- Hybrid module

- Multi chip module

- Feedback techniques

- Self-oscillating topologies

- Digital domain PWM

processing

Higher Performance + Smaller Size + Lower Cost

At The Same Time !

# 1. MOSFET Technology Trend

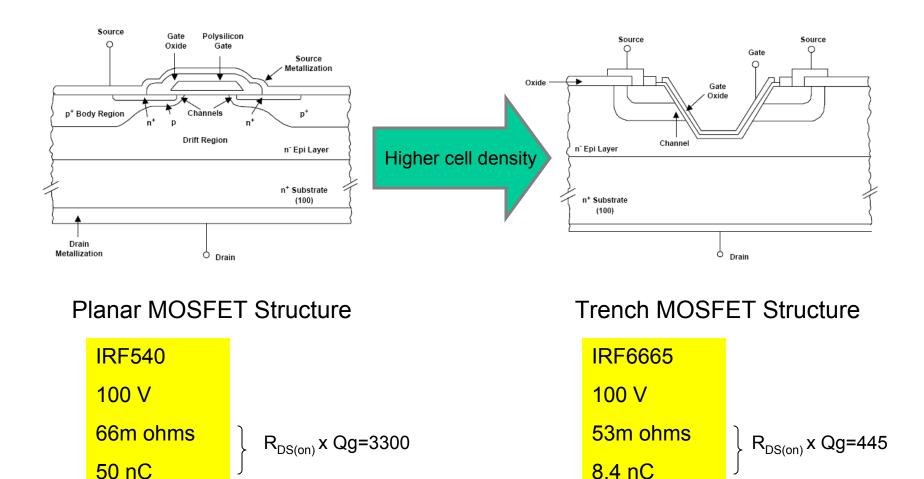

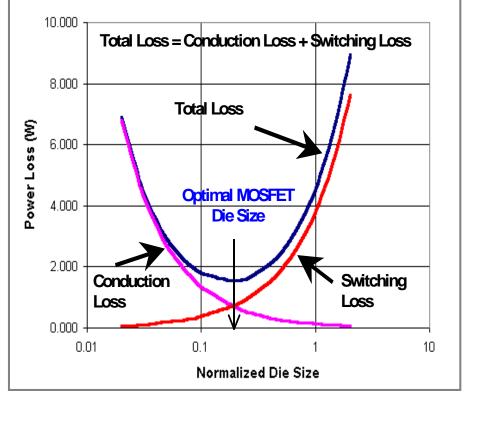

A MOSFET has inherent trade-offs between ON resistance and gate charge,  $R_{DS(on)}$  vs Qg. In device design, this translates into Conduction loss vs Switching loss trade-off.

The objective of optimization for Class D applications is to achieve minimal power loss.

Newer platforms show better FOM (Figure of Merit)

➔ This is what makes Class D keep improving!

2002

Fiscal Year

Trench Technology

2003

International Rectifier Mosfet R\*Qg Trend

2001

IR Mosfet Technology Constant Improvement

1.2

0.9

80.0 80 8

**12** 0.7

**2** 0.6

0.5 0.4 0.3

0.2

2004

2005

#### The latest trench MOSFET technology shows 7 times better figure of merit.

**IGR** International Rectifier

There is a best die size for a given output power. Optimum die size for minimal  $P_{LOSS}$  depends on load impedance, rated power and switching frequency.

A more advanced platform with better FOM acheives lower  $P_{LOSS}$ .

To learn more about MOSFET selection, refer to

AN-1070 Class D Amplifier Performance Relationship to MOSFET Parameters.

Trade-offs in MOSFET Design

Optimal MOSFET die size  $\Rightarrow$  Optimal MOSFET Parameters

How the package affects the design?

#### 1. Amplifier size

- Increase efficiency

- Increase current capability

- Improve the MOSFET thermal efficiency

#### To utilize benefits from a newer generation MOSFET, new package with reduced stray inductance is necessary.

# S1/D2 ⇒ Better control of current and voltage 5 PIN TOP SIDE OF CAN IS NI ONLY

transients

2. EMI considerations

- 3. Amplifier linearity

- Decrease switching times

- Narrow the MOSFET parameter distribution

A MOSFET has capacitive elements.

Stray inductance is where excessive energy is stored, causing over/under shoots and rings.

Stray inductance in Source returns feedback voltage to gate, slowing down switching speed significantly.

The smaller the parasitic components the better performance!

To learn more about MOSFET switching behavior, refer to AN-947 Understanding HEXFET Switching Performance.

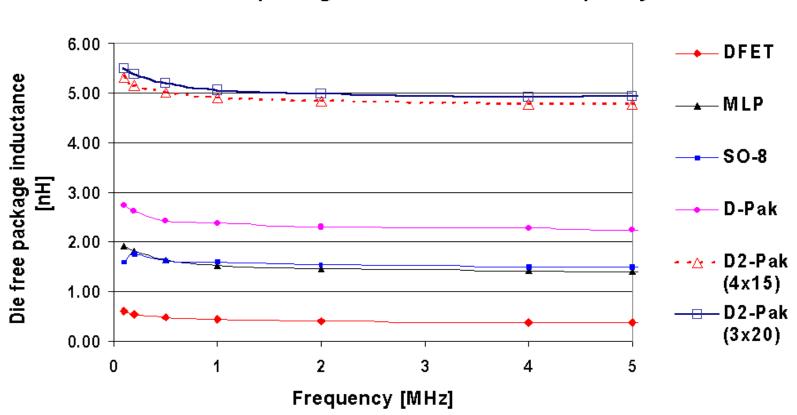

Die free package inductance versus frequency

- Lower inductance at frequency than SO-8, D-Pak, MLP and D-Pak

- TO-220 inductance package is ~ 12nH

- DirectFET<sup>®</sup> is 0.4nH

**IGR** International Rectifier

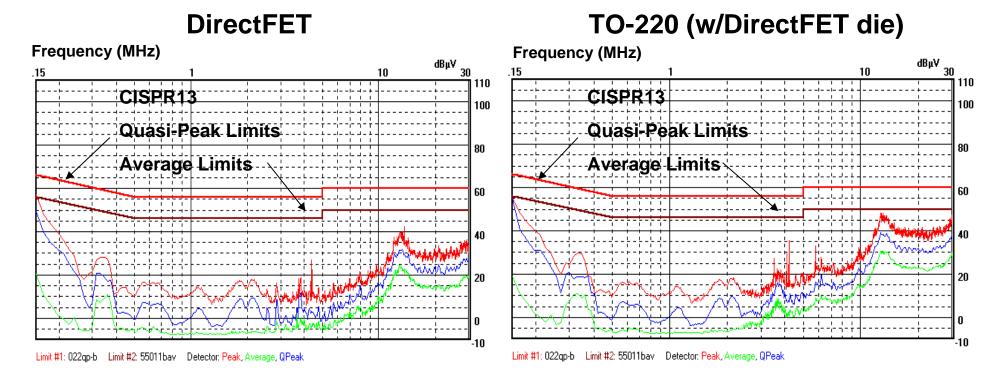

- DirectFET<sup>®</sup> amplifier shows better EMI performance than TO-220 amplifier

- •Over 2MHz, DirectFET amplifier shows approximately 9dBuV lower Peak, Quasi-Peak and Average noise than TO-220 amplifier

- •Both PCB's meet audio amplifier EMI standards limits (CISPR13)

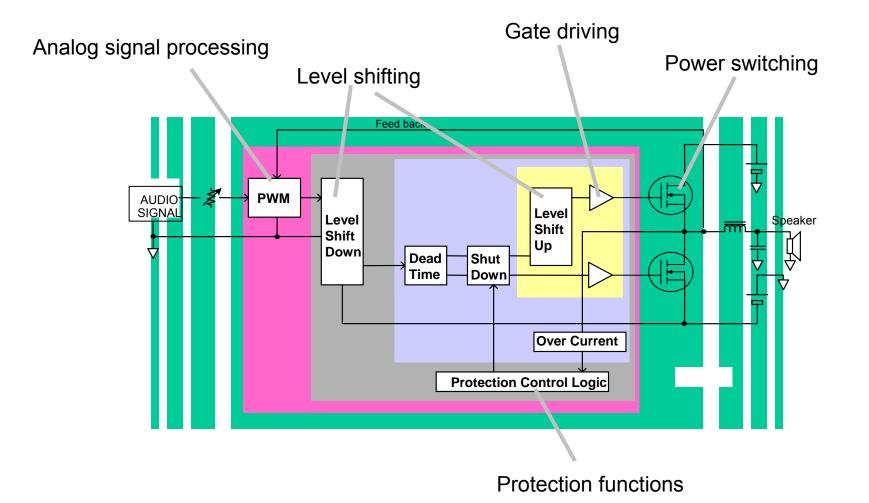

• More integration to realize smaller footprint

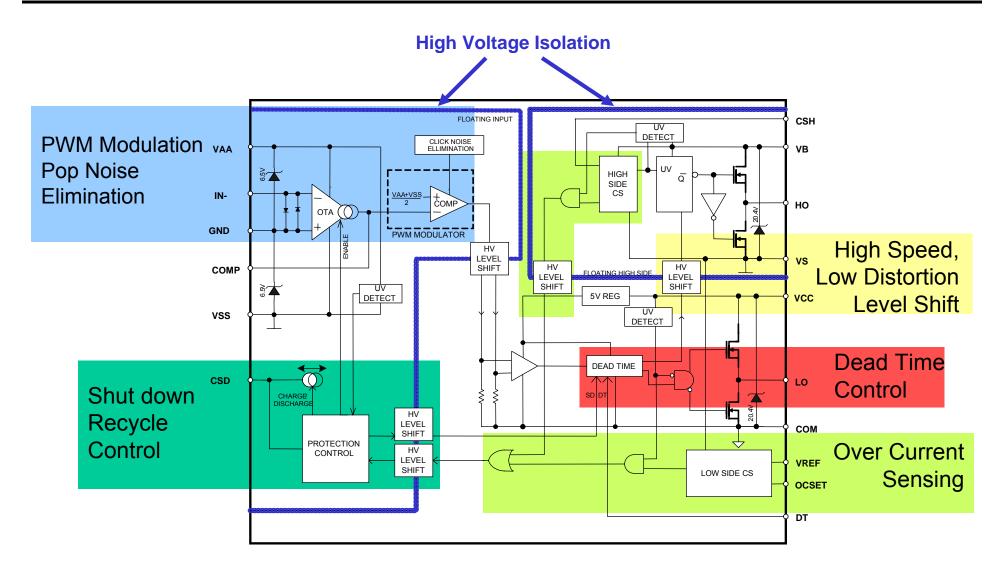

#### **Four Essential Functions in Gate Driver IC**

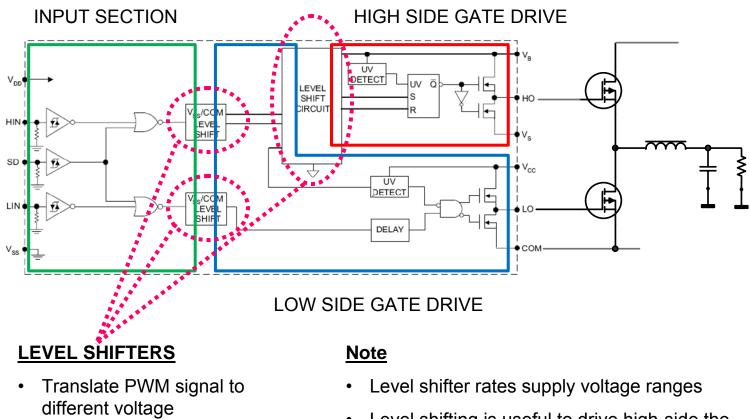

Level Shift

• Gate Drive

• Deadtime Generation

• Under Voltage Lockout

To learn more about High Voltage Gate Driver IC, refer to AN-978 HV Floating MOS-Gate Driver ICs.

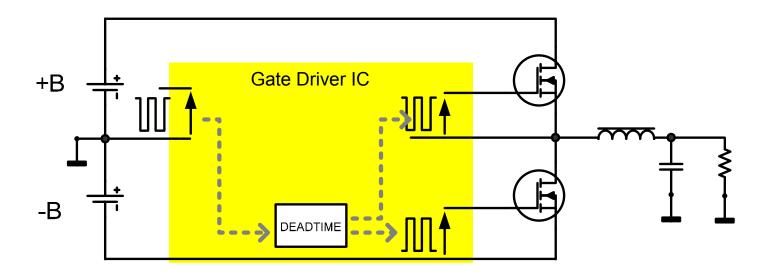

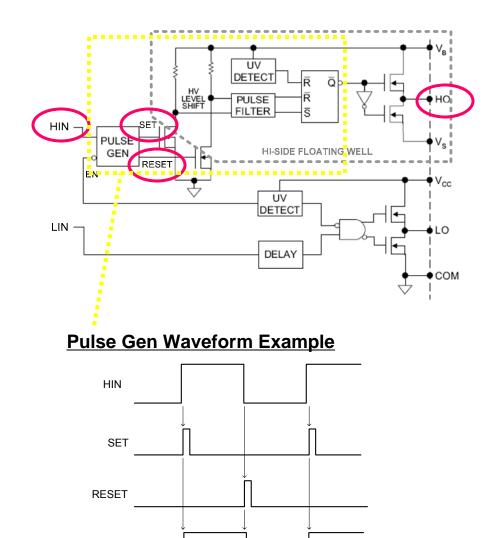

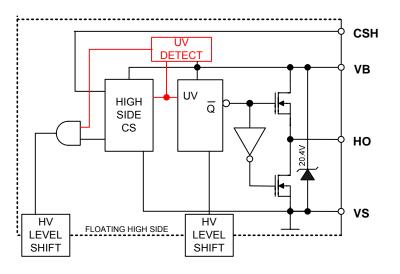

#### **Operation Principle**

A pair of SET and RESET signals are generated at the PULSE GEN block.

The SET and RESET pulses drive the high voltage MOSFET to send these signals to circuitries in a floating high-side well.

The high-side circuitry reconstructs PWM from SET and RESET pulses.

This method minimizes power dissipation in the high voltage MOSFETs in level shifter.

HO

- potential

- Isolate circuit blocks that are in different voltage potentials

- Level shifting is useful to drive high-side the MOSFET whose source is tied to switching node.

- Level shifting blocks switching noise coming into sensitive input section.

**ICR** International Rectifier

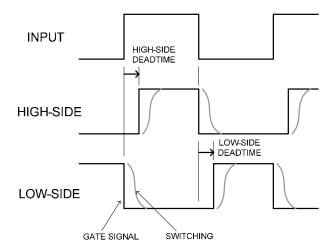

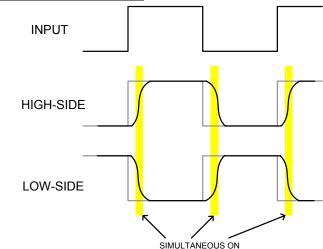

With Dead-time

Without Dead-time

Dead-time (or blanking time) is a period of time intentionally inserted in between the ON states of high- and low-side MOSFETs.

This is necessary because the MOSFET is a capacitive load to the gate driver that delays switching time and causes simultaneous ON.

Lack of dead-time results in lower efficiency, excessive heat and potential thermal failure.

Usually, dead-time is realized by delaying turn on timing.

**IOR** International Rectifier

- Under voltage lockout (UVLO) prevents the MOSFET from entering the "half-ON" region when the gate bias voltage is reduced.

- The "half-ON" condition of the MOSFET creates excessive power loss due to increased R<sub>DS(on)</sub> that could lead to MOSFET failure, therefore must be avoided.

- During the UVLO, gate drive stage keeps HO/LO low in order to prevent unintentional turn-on of the MOSFETs.

- UVLO in  $V_{CC}$  resets shutdown logic and causes CSD recycling to start over the power up sequence.

- The IR Class D audio gate driver family is designed to accept any power sequence.

UVLO of VBS shuts down HO and disable high-side current sensing

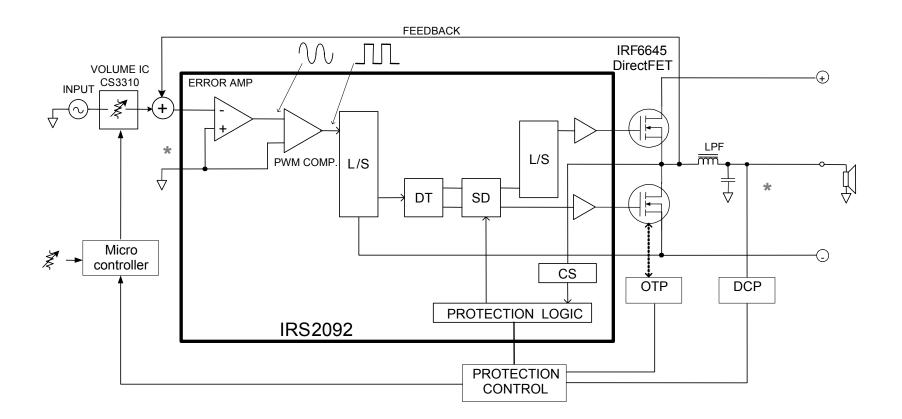

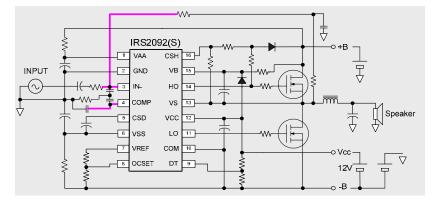

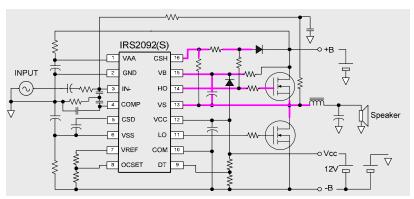

# Inside of High Voltage Gate Driver IRS2092

#### **PWM modulator's functions**

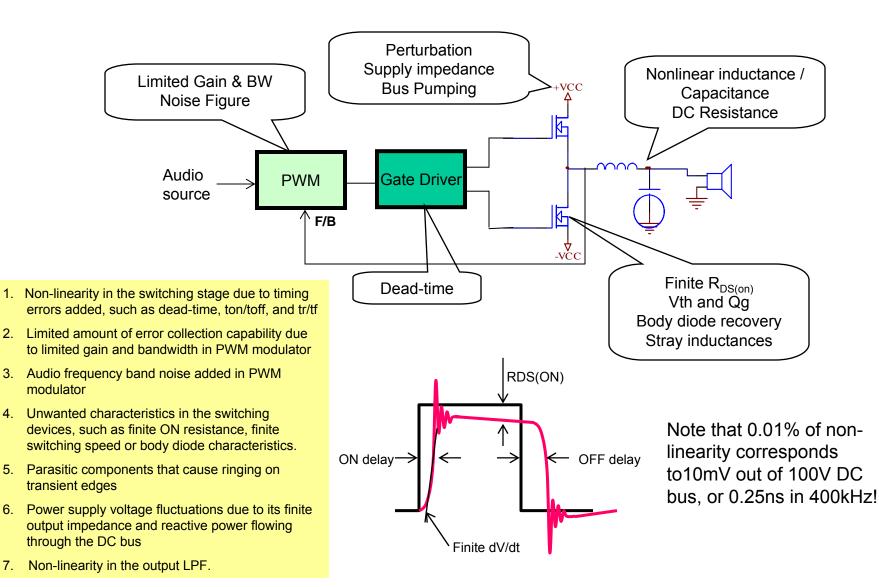

- Convert analog or digital audio signal (PCM) to PWM that has reasonable switching frequency for power MOSFET

- Error corrections to improve audio performance

#### **Demands**

- Feedback to reduce DC offset, distortion and noise floor

- Larger loop gain for lower distortion, higher power supply rejection ratio (PSRR)

- Post filter feedback for higher damping factor

- Switching frequency control for reduced EMI

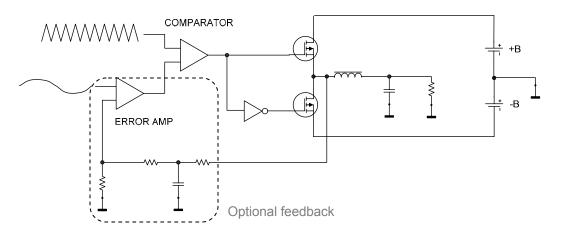

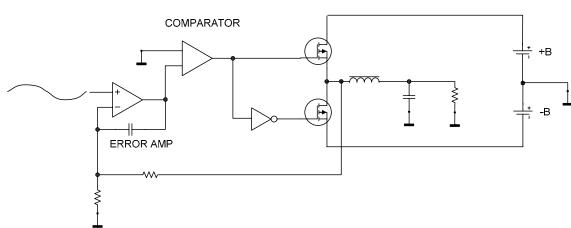

#### Natural PWM

- Open loop or closed loop

- Fixed frequency

### Self-oscillating PWM

- Closed loop

- Frequency changes with modulation

- High loop gain

- Fewer components

**IOR** International Rectifier

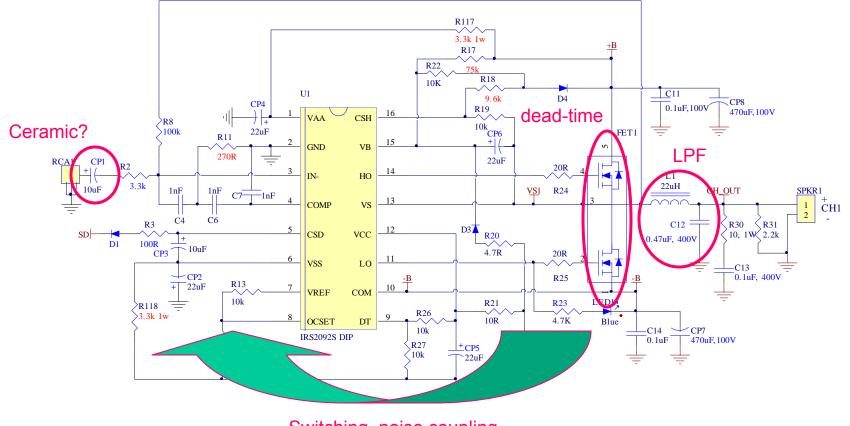

Typical IR audio evaluation board based on self-oscillating PWM with 2<sup>nd</sup> order integration

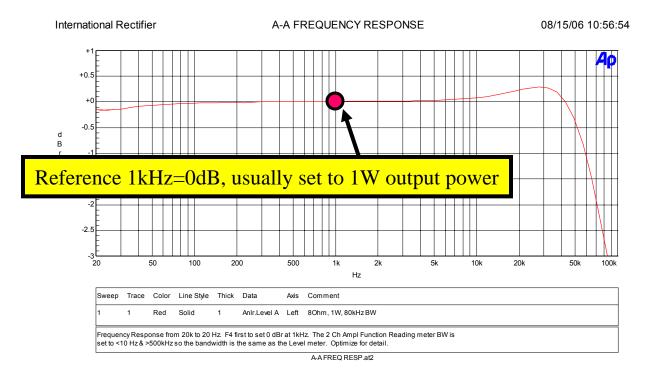

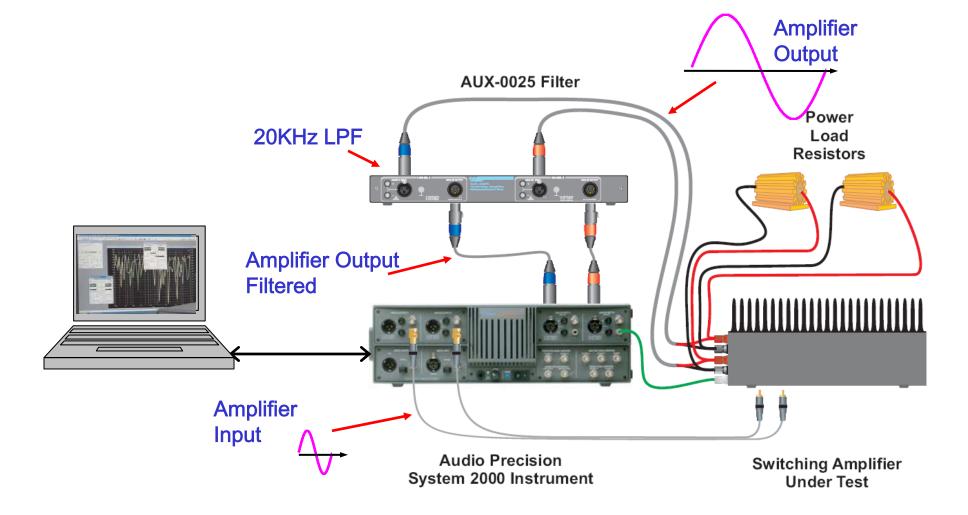

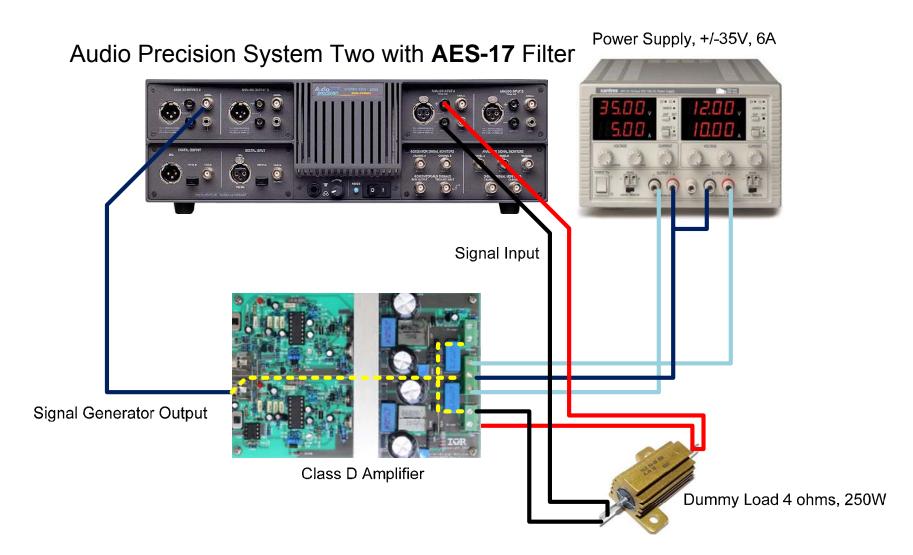

## Chapter 3: Identifying Problems ~ Performance Measurement of Class D Amplifier

- Proper audio performance measurement is crucial to identify potential problems.

- Frequency response and THD+N are the minimum basic measure of audio performance.

| Problem                  | Possible Causes                                    |

|--------------------------|----------------------------------------------------|

| Low frequency response   | Audio input, feedback network                      |

| High frequency response  | Audio input, feedback network,<br>LPF design       |

| High harmonic distortion | Shoot-through, dead-time, switching noise coupling |

| High noise floor         | Analog input, switching noise coupling             |

## **1. Frequency Response**

- Use resistive dummy load.

- Set reference voltage level to 1W output power at 1kHz.

- Sweep sinusoidal signal from 20Hz to 100kHz.

- Take frequency response with various load impedances and without loading.

. .

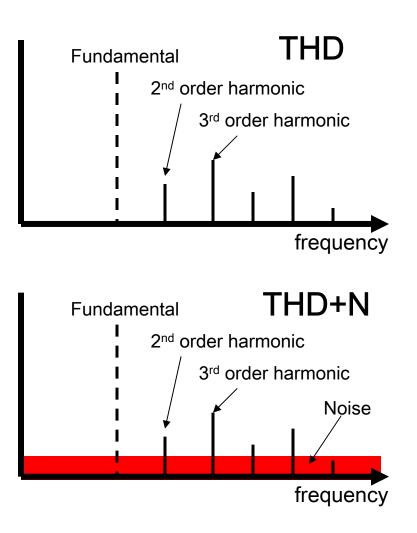

## 2: THD+N

- THD+N is a sum of harmonic distortion components and noise, i.e. anything except fundamental spectrum.

- THD is a measure of linearity.

- ➔ Refer to Chapter 4

- Noise is a measure of added errors not depending on the input signal

- → Refer to Chapter 5

Frequency

True cause of distortion

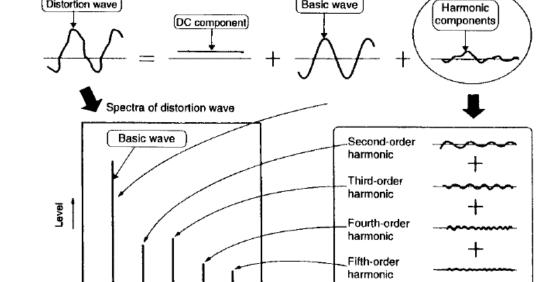

Any repetitive waveforms can be expressed as a sum of sinusoidal signal as

$$V_o = dc + \sum_{n=1}^{\infty} A_n \cdot \sin(nwt + \theta_n)$$

Harmonic distortion is a ratio of rms value of the harmonic component and the original waveform.

$HDn = A_n / A_t$

Total harmonic distortion is a ratio of rms value of sum of the all harmonic component and the original waveform.

$$THD = \sqrt{\left(\sum_{n=2}^{\infty} HDn^2\right)}$$

Can be divided into the sum of

sine waves.

• If the amplifier is not linear, it generates harmonics.

Basic wave

Distortion wave

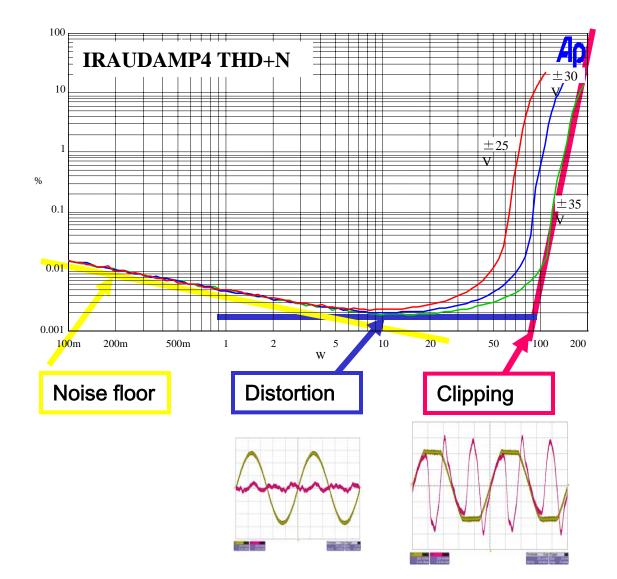

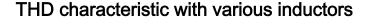

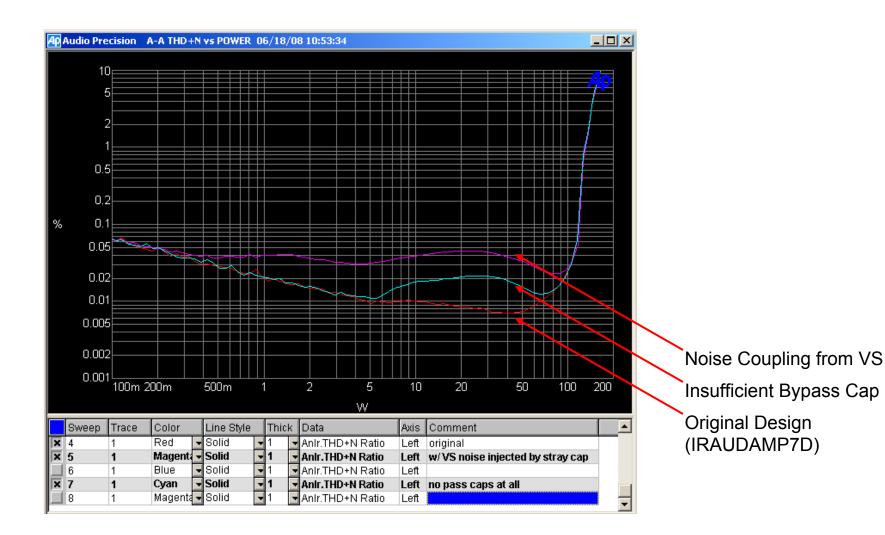

- THD+N vs. Power spells out noise floor, distortion and output power in a shot.

- Noise floor dominant part has 20dB/dec slope.

- Reading above noise floor slope is dominated by harmonic distortion.

- To trouble shoot, better to start with single channel operation.

Switching noise coupling

. .

For more information on Class D audio measurement, refer to white paper, Measuring Switch-mode Power Amplifiers by Bruce Hofer, from //ap.com

**I**R International Rectifier

### **AP Substitute**

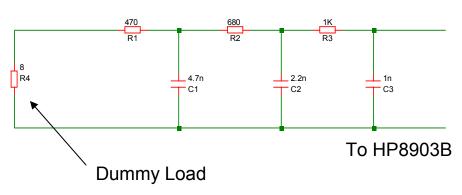

- Old audio analyzers are not designed to tolerate high frequency noise that is from carrier signal residual from a Class D amplifier.

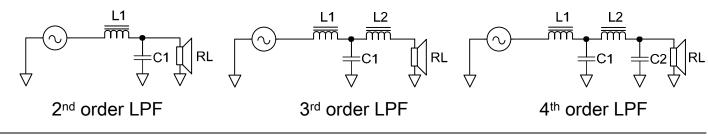

- Place a 3<sup>rd</sup> order LPF to remove the switching carrier ingredients in front of the audio analyzer

- Check measurements are correct by changing scaling range manually

An Example of an additional pre-LPF for HP8903B

**ISR** International Rectifier

## Chapter 4: Reducing Distortion ~dead-time ~ LPF Designs

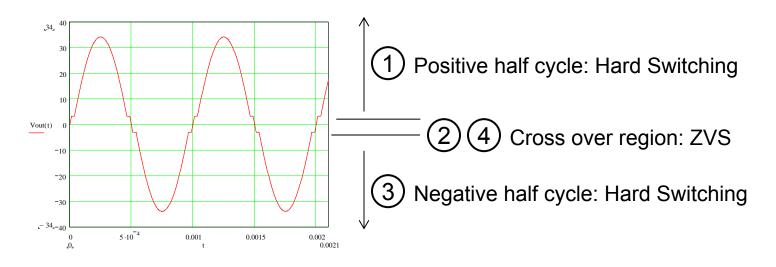

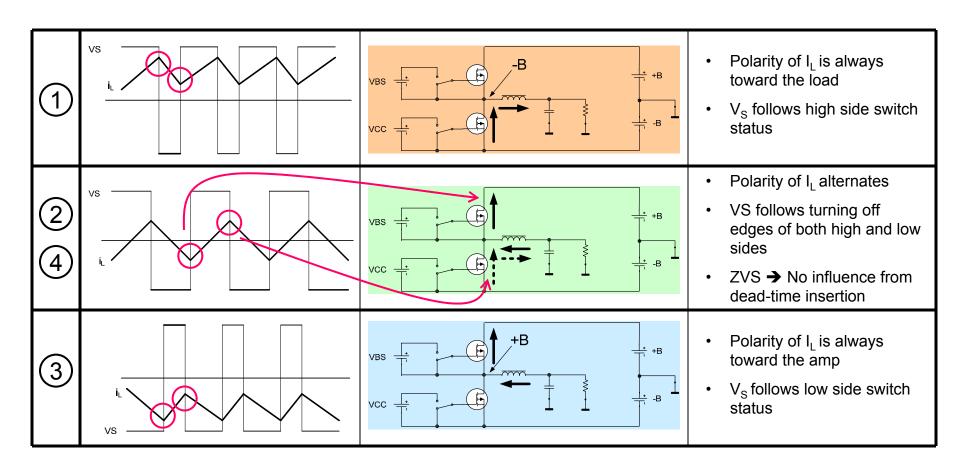

- Dead-time reduces volt-second therefore voltage gain.

- There is a region that dead-time does not affect around zero crossing (regions 2 and 4).

- The smaller the dead-time, the lower the distortion.

- Too narrow dead-time could cause shoot-through from unit-to-unit, temperature and production variations, that could seriously affect product reliability.

- Audio performance and reliability is NOT a trade-off.

**ICR** International Rectifier

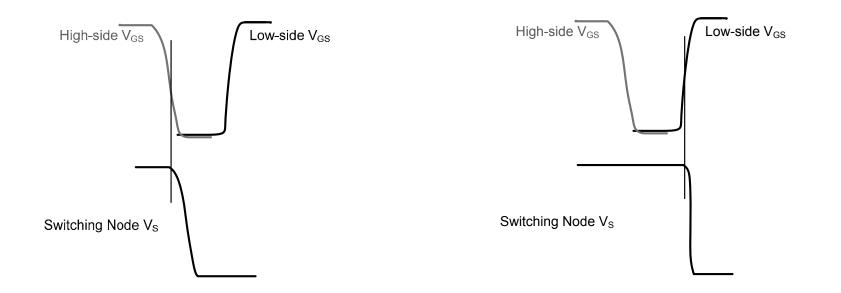

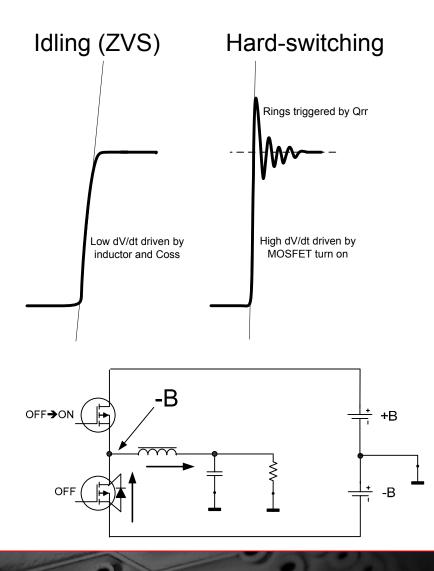

#### **ZVS Region**

Turning off of the previous MOSFET dictates transition in switching waveform.

#### Hard Switching Region

Turning on dictates output switching waveform.

**IOR** International Rectifier

### **During Dead-time**

Note: Dead-time insertion reduces volt-second of  $V_s$ . Dead-time inserted in the rising edge of the high side affects the operating region 1. Dead-time inserted in the rising edge of the low side affects the operating region 3. As a result, output voltage gets lower than it should be, causing non-linearity in the output stage.

٠

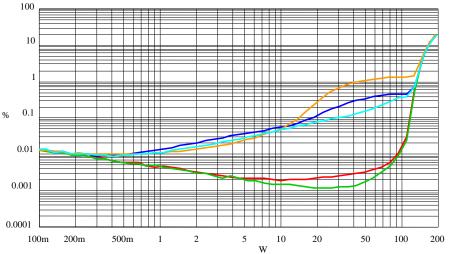

### also efficiency. Inductance changes with load current, which causes distortion.

Trade-off 2: Inductor and Distortion

• Core saturation increase inductor ripple significantly that can trigger over current protection.

The quality of the output inductor

target audio performance but

is crucial to achieve not only the

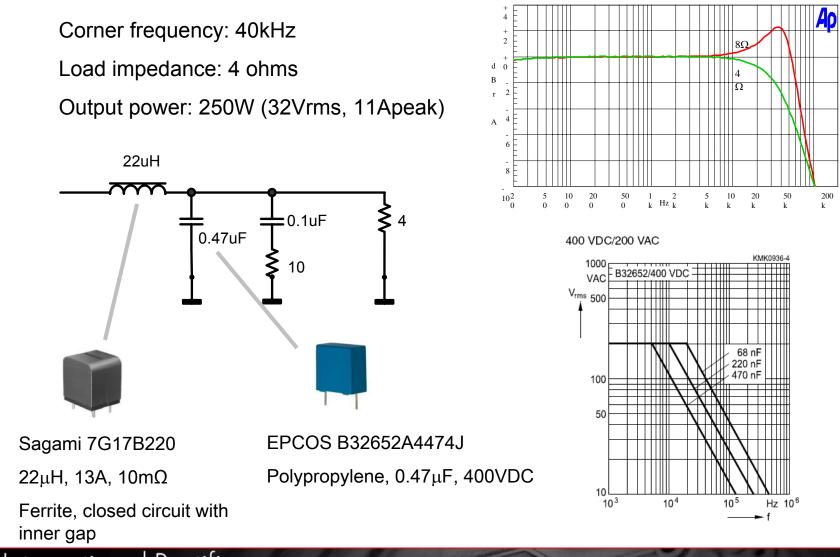

# LPF Design

- Set corner frequency according to the bandwidth requirement.

- Design LC-LPF with Q=0.7 for a nominal load impedance to attain flat frequency response.

#### Inductance and inductor ripple

$$I_{LPP} = \frac{Vbus}{L \cdot f_{SW}}$$

#### Inductor ripple current dictates ZVS region

#### Note that

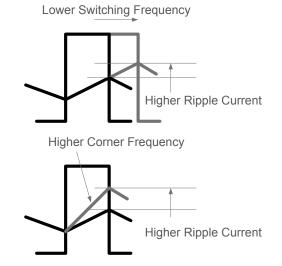

- The higher the corner frequency the higher the switching carrier leakage

- The lower the corner frequency the bigger the inductance size

# LPF Design

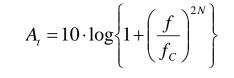

1. Decide the order of the filter based on the attenuation of the switching frequency given by:

2. Design Butterworth filter

$$L_n = \frac{R_L}{2 \cdot \pi \cdot f_C} L k_n$$

$$C_n = \frac{C k_n}{2 \cdot \pi \cdot f_C \cdot R_L}$$

| # of Order | Lk1      | Ck1      | Lk2      | Ck2      |

|------------|----------|----------|----------|----------|

| 2          | 1.414214 | 0.707107 | -        | -        |

| 3          | 1.5000   | 1.3333   | 0.5000   | -        |

| 4          | 1.530734 | 1.577161 | 1.082392 | 0.382683 |

|            |          |          |          |          |

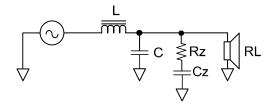

3. Design Zobel network

| Air Coil                               | Large, High DCR, Low<br>distortion, Leakage flux |

|----------------------------------------|--------------------------------------------------|

| Drum Core<br>(Ferrite, Open Circuit)   | Small, Leakage Flux, Low DCR                     |

| Drum Core<br>(Ferrite, Closed Circuit) | Small, Hard saturation, Low<br>DCR               |

| Toroidal Core<br>(Iron Powder)         | Soft saturation, Lower iron loss                 |

NOTE

- Ferrite core is suitable for smaller size

- Iron powder is suitable for high power

- Determine I<sub>RMS</sub> rating for temperature rise condition with 1/8 rated power

- Determine peak current (I<sub>SAT</sub>) based on maximum load current

### **IGR** International Rectifier

| 138 - C                            | Polyester film, winding      | Small, High ESR                                             |

|------------------------------------|------------------------------|-------------------------------------------------------------|

|                                    | Ceramic                      | High dielectric type has large distortion, lower AC ratings |

| WIMA<br>MKS 4<br>0,047/250-        | Polyester, non-inductive     | Small, lower AC voltage rating                              |

| WIMA [0,022<br>FKP 1 1600-<br>650~ | Polypropylene, non-inductive | Low dissipation factor, large size, low distortion          |

NOTE

- Do not use winding structure types. Use stacked structure.

- Check AC voltage ratings at highest audio frequency.

**ISR** International Rectifier

## Chapter 5: Reducing Noise ~ Noise Isolation Technique ~ PCB Design

#### Switching noise

Switching noise is generated by the output MOSFET switching in wide range of frequency spectrum above the audible range. The amount of switching noise depends on:

- Switching speed

- Size of the MOSFET

- Load current

- PCB layout

- Locations and quality of bypass capacitors

#### Audio noise

Audio noise is a noise ingredient in audible frequency range in the speaker output. Major causes of audio noise includes:

- Noise figure (NF) in the front-end error amplifier

- Jitter in switching time

- RFI noise from switching noise injection

- Thermal noise from resistors

- Hum noise (AC line 60Hz and its harmonics) from ground loop

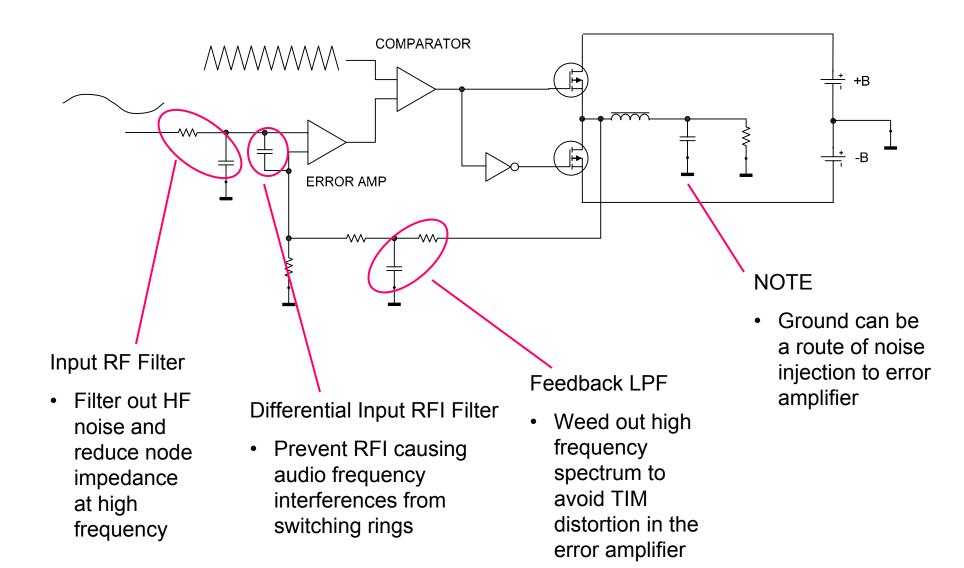

- **1. Minimize noise source in switching stage**

- 2. Maximize noise immunity in analog stage

- 3. Minimizing noise coupling from switching stage to analog stage

Self-commutation at idling. If rings, check for shoot-through, check dead time.

Reverse recovery charge, Qrr, causes hard switching that triggers resonance in stray reactance.

Qrr is a function of di/dt, drain current and die temperature. Slower switching helps to reduce Qrr.

Stray inductance is where excessive energy is stored. Look for optimum trace layouts to minimize stray inductance.

Careful component selection is key to minimize stray reactance.

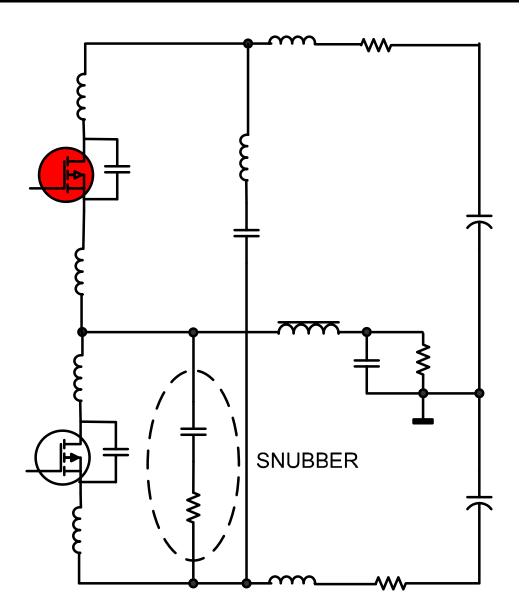

### Reducing Noise with RC Snubber

RC voltage snubber is used to suppress voltage spikes in switching and power supply nodes.

Resistor in RC snubber absorbs energy from reactance by damping resonance.

To maximize effectiveness of a snubber

- Resistance should be close to impedance of resonant element.

- Capacitance should be larger than resonant capacitor.

- Capacitance should be small enough not to cause too much dissipation in the resistor.

Power dissipation from the resistor

$$P= 2^{f^{(1)}/2}CV^{2})$$

#### **IGR** International Rectifier

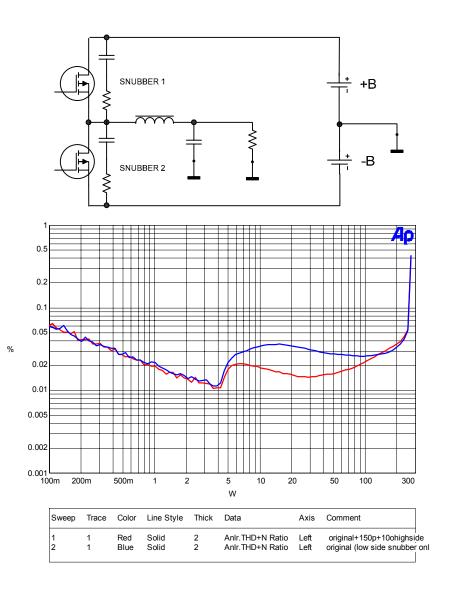

# Snubber and THD

Adding snubber usually improves THD+N.

Change should be in hard switching region.

Basic approach: Make all efforts to minimize stray inductances and current loop areas (minimize resonant energy), then tailor snubber values.

Pay attention to dissipation at snubber.

# RFI

Analog stage uses non-linear components such as diode, BJT and FET.

When a non-linear component receives high frequency components, it detects envelop information that could fall into audio frequency range (amplitude modulation envelop detector).

When non-linear components receives high frequency components along with audio signal, it could shift operating bias point and cause distortion in audio signal. **Diode amplitude detector**

**I**

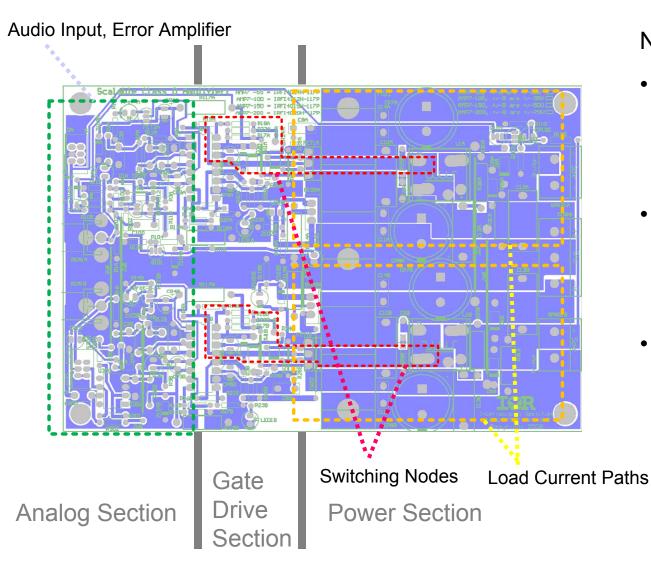

### **3: Minimizing Noise Coupling**

There are functional blocks that generate noise. There are functional blocks that are sensitive to noise. The PCB designer should identify them and find out the best combination of the placement based on these facts and mechanical and thermal requirements.

Noise sensitive functions:

- The audio input circuitry

- The PWM control circuitry

- Noise generating functions

- The gate driver stage

- The switching stage

#### **Noise Sensitive Nodes**

#### **Noise Generating Nodes**

The first and most important step for PCB designers is to group components dedicated to a common purpose, such as:

- the audio input circuitry

**PCB Design Tips**

- the PWM control circuitry

- the gate driver stage

- the switching stage

By identifying which components belong together, place the remaining circuitry by coupling them appropriately into open areas of the board.

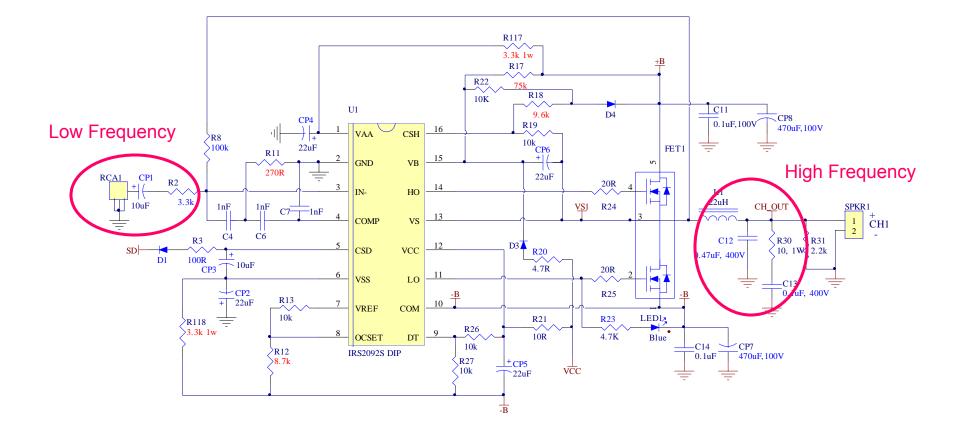

# Key Components Layout Example (IRAUDAMP7D)

Placement Determines Maximum Performance !

#### Note that

- Separation between analog and switching sections

- Minimized trace impedances with planes in power section

- No overlap between switching nodes and analog nodes

.....

### APPENDIX

**IGR** International Rectifier

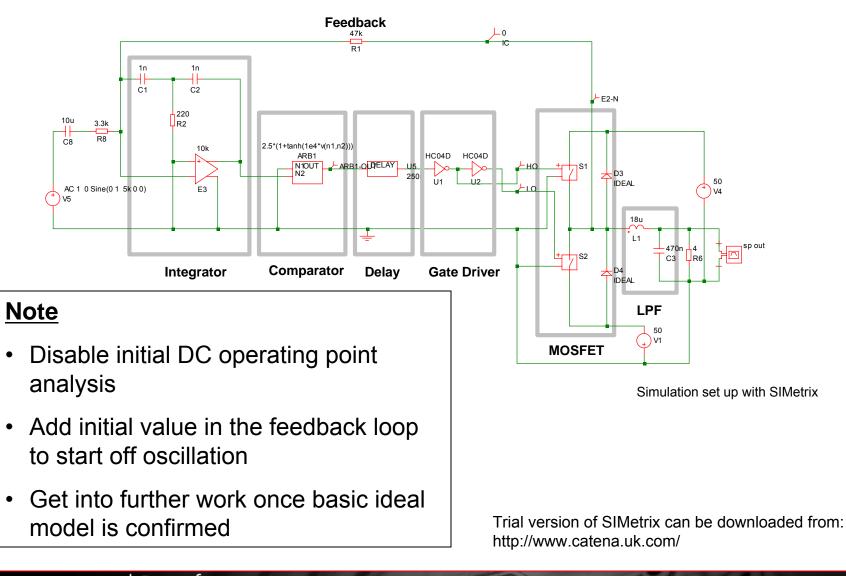

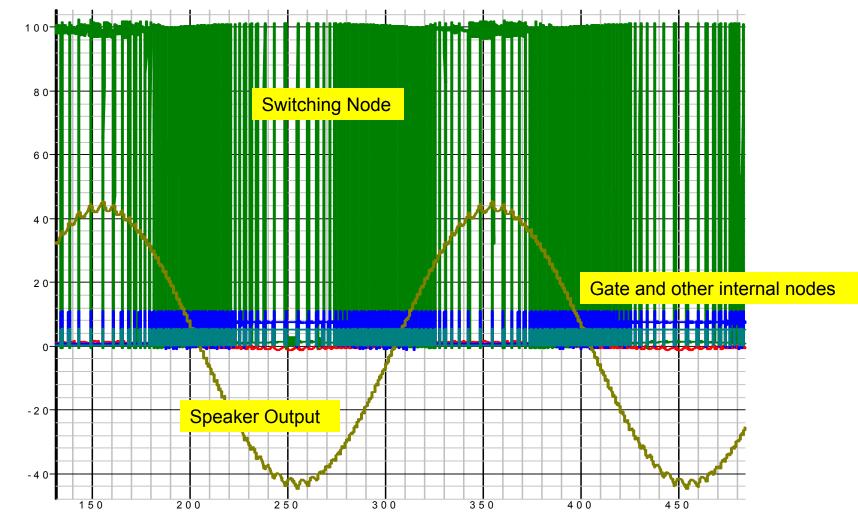

# Simulation of a Simple Class D Amplifier (SIMetrix)

**ICR** International Rectifier

Tim e / µ S e c s

50µSecs/div

**I**

>

END

February 19, 2009

.....

**IGR** International Rectifier