# CPU\_Trap\_Recognition\_1 for KIT\_AURIX\_TC375\_LK TRAP error recognition and reaction

AURIX™ TC3xx Microcontroller Training V1.0.0

# Scope of work

# This example shows how to identify the root cause of a trap.

The tutorial describes what types of traps are supported by the AURIX™ microcontroller, their root causes and how to identify them. AURIX™ architecture supports different types of traps. Three different traps can be provoked with this example and the tutorial guides the user through the needed steps to observe the root cause of each trap.

# Introduction

- A trap occurs as a result of an event such as a Non-Maskable Interrupt (NMI), an instruction exception, a memory management exception or an illegal access. Traps are always active; they cannot be disabled by software.

- The TriCore™ architecture specifies eight general classes for traps. Each trap class has its own trap handler. Within each class, specific traps are distinguished by a Trap Identification Number (TIN).

- Traps can be further classified as synchronous or asynchronous, and as hardware or software generated.

- > Three different combinations of trap types are supported:

- Synchronous and hardware generated

- Asynchronous and hardware generated

- Synchronous and software generated

# Hardware setup

This code example has been developed for the board KIT\_A2G\_TC375\_LITE.

### **Supported traps**

The following table provides an overview about all supported traps and their types:

| TIN   | Name      | Synch. /<br>Asynch. | HW /<br>SW | Definition                               |

|-------|-----------|---------------------|------------|------------------------------------------|

| Class | 0 — MMU   | '                   |            |                                          |

| 0     | VAF       | Synch.              | HW         | Virtual Address Fill.                    |

| 1     | VAP       | Synch.              | HW         | Virtual Address Protection.              |

| Class | 1 — Inter | nal Protectio       | n Traps    |                                          |

| 1     | PRIV      | Synch.              | HW         | Privileged Instruction.                  |

| 2     | MPR       | Synch.              | HW         | Memory Protection Read.                  |

| 3     | MPW       | Synch.              | HW         | Memory Protection Write.                 |

| 4     | MPX       | Synch.              | HW         | Memory Protection Execution.             |

| 5     | MPP       | Synch.              | HW         | Memory Protection Peripheral Access.     |

| 6     | MPN       | Synch.              | HW         | Memory Protection Null Address.          |

| 7     | GRWP      | Synch.              | HW         | Global Register Write Protection.        |

| Class | 2 — Instr | uction Errors       |            |                                          |

| 1     | IOPC      | Synch.              | HW         | Illegal Opcode.                          |

| 2     | UOPC      | Synch.              | HW         | Unimplemented Opcode.                    |

| 3     | OPD       | Synch.              | HW         | Invalid Operand specification.           |

| 4     | ALN       | Synch.              | HW         | Data Address Alignment.                  |

| 5     | MEM       | Synch.              | HW         | Invalid Local Memory Address.            |

| Class | 3 — Conto | ext Managem         | ent        |                                          |

| 1     | FCD       | Synch.              | HW         | Free Context List Depletion (FCX = LCX). |

| 2     | CDO       | Synch.              | HW         | Call Depth Overflow.                     |

| 3     | CDU       | Synch.              | HW         | Call Depth Underflow.                    |

| TIN   | Name      | Synch. /<br>Asynch.  | HW /<br>SW | Definition                                   |

|-------|-----------|----------------------|------------|----------------------------------------------|

| 4     | FCU       | Synch.               | HW         | Free Context List Underflow (FCX = 0).       |

| 5     | CSU       | Synch.               | HW         | Call Stack Underflow (PCX = 0).              |

| 6     | CTYP      | Synch.               | HW         | Context Type (PCXI.UL wrong).                |

| 7     | NEST      | Synch.               | HW         | Nesting Error: RFE with non-zero call depth. |

| Class | 4 — Syste | m Bus and Pe         | eripheral  | Errors                                       |

| 1     | PSE       | Synch.               | HW         | Program Fetch Synchronous Error.             |

| 2     | DSE       | Synch.               | HW         | Data Access Synchronous Error.               |

| 3     | DAE       | Asynch.              | HW         | Data Access Asynchronous Error.              |

| 4     | CAE       | Asynch               | HW         | Coprocessor Trap Asynchronous Error.         |

| 5     | PIE       | Synch                | HW         | Program Memory Integrity Error.              |

| 6     | DIE       | Asynch               | HW         | Data Memory Integrity Error.                 |

| 7     | TAE       | Asynch               | HW         | Temporal Asynchronous Error                  |

| Class | 5— Asser  | tion Traps           |            |                                              |

| 1     | OVF       | Synch.               | SW         | Arithmetic Overflow.                         |

| 2     | SOVF      | Synch.               | SW         | Sticky Arithmetic Overflow.                  |

|       | 1         |                      | '          |                                              |

| Class | 6 — Syste | m Call <sup>1)</sup> |            |                                              |

|       | SYS       | Synch.               | SW         | System Call.                                 |

| Class | 7 — Non-  | Maskable Inte        | errupt     |                                              |

| 0     | NMI       | Asynch.              | HW         | Non-Maskable Interrupt.                      |

Please refer to the TriCore™ TC1.6.2 core architecture manual and the AURIX™ TC3xx User's Manual for detailed information about each trap.

### **Trap types**

### Synchronous traps:

- Synchronous traps are associated with the execution or attempted execution of specific instructions or with attempts to access a virtual address that requires the intervention of the memory-management system.

- The trap is triggered and serviced immediately.

### Asynchronous traps:

- Since asynchronous traps are associated with hardware conditions, they are similar to interrupts.

- They are routed via the trap vector.

- Some asynchronous traps are triggered indirectly from instructions, that have been previously

executed, but the direct association with the instructions causing the trap is lost.

### Hardware traps:

- Hardware traps are generated in response to exception conditions detected by the hardware.

- In most, but not all cases, the exception conditions are associated with the attempted execution of a particular instruction.

### Software traps:

Software traps are generated as an intentional result of executing a system call or an assertion instruction.

### **Trap handling**

- When a trap occurs, a trap identifier is generated by hardware. The trap identifier has two components that can be used to determine more information about the trap and why it was caused (refer to slide <u>Supported traps</u>):

- The Trap Class Number (TCN)

- The Trap Identification Number (TIN)

- In most cases, the debugger will stop the code execution within one of the trap handlers (implemented in the iLLD header IfxCpu\_Trap.c)

- An instance of the structure *IfxCpu\_Trap* is declared within each trap handler. When a trap occurs, the instance provides four information fields about the trap:

- tCpu: Which CPU caused the trap

- tClass: TCN, Class of the trap (refer to slide Supported traps)

- tld: TIN, Id of the trap (refer to slide <u>Supported traps</u>)

- tAddr: Return Address (RA) (refer to the <u>next slide</u>)

### **Return Address**

- The Return Address (RA) might help to locate the specific line of code which caused the trap.

- The return address, which is stored in the instance of the *IfxCpu\_Trap* structure, is read from the return address register A[11].

- > Depending on the **trap type**, the return address is different:

- For most of the synchronous traps, the return address is the 32-bit Program Counter (PC) of the instruction that caused the trap. (The PC holds the address of the instruction which is currently running when the core is halted.)

- On a System Call (SYS) trap, triggered by the SYSCALL instruction, the return address

points to the instruction immediately following SYSCALL.

- A Free Context List Depletion (FCD) trap is generated after a context save operation that causes the free context list becoming "almost empty".

The responsible for the FCD trap can be a hardware interrupt or a trap handler. The operation responsible for the context save normally is completed before the FCD trap is executed. Because of this, the return address of the FCD trap is the first instruction of the trap/interrupt/called routine or the instruction following a Save Lower Context (SVLCX) or Begin Interrupt Service Routine (BISR) instruction.

- For an asynchronous trap, the return address is the address of the instruction that would have been executed next, if the asynchronous trap had not been triggered.

### Additional debug information

- The bit field ERROR\_ADDRESS of the **Data Error Address Register (DEADD)** contains the trap address information for the data memory. The content of the DEADD register is valid if the **Data Synchronous Trap Register (DSTR)** or the **Data Asynchronous Trap Register (DATR)** register are non-zero (depending on the trap type). The bit fields in the DSTR and the DATR registers can provide additional information about the trap (refer to the AURIX™ TC3xx User's Manual).

- These information are valid in case traps such as:

- Data Address Alignment (ALN)

- Data Access Synchronous Error (DSE)

- Data Access Asynchronous Error (DAE)

- Invalid Local Memory Address (MEM)

- Memory Protection Write (MPW)

- Memory Protection Read (MPR)

- Memory Protection Peripheral Access (MPP)

- Memory Protection Null Address (MPN)

### Additional debug information

- The Program Memory Interface Synchronous Trap Register (PSTR) contains synchronous trap information for the program memory system. The register is updated with trap information for Program Fetch Synchronous Error traps (PSE).

- The Program (or Data) Integrity Error Address Register (PIEAR / DIEAR) and the Program (or Data) Integrity Error Trap Register (PIETR / DIETR) can be interrogated to determine the source of the Program (or Data) Memory Integrity Error (PIE / DIE) more precisely.

### **Trap provocation**

- > Three different combinations of trap types can be provoked in this example:

- Synchronous Hardware trap

- Asynchronous Hardware trap

- Synchronous Software trap

- The trap provocation is implemented in the function run\_trap\_provocation() and can be started by setting one of the three g\_provokeXYTrap (X = Synchronous / Asynchronous; Y = Hardware / Software) variables.

- > The implemented code for the first two traps is based on the MTU\_MBIST\_1 and SMU\_IR\_Alarm\_1 examples. For further information on the code, please refer to the specific tutorials.

- The third trap is provoked by using two instructions: \_\_mtcr() (Move To Core Register) and trapv (assembly code). For further information on these instructions, please refer to the TriCore™ TC1.6.2 core architecture manual Instruction set manual.

**Note:** \_\_*mtcr()* is an intrinsic function of the Tasking compiler, which moves contents of a data register to the addressed Core Special Function Register (CSFR). \_\_*mtcr()* performs a Move to Core Register (*MTCR*) TriCore<sup>™</sup> instruction and is followed by an *ISYNC* instruction.

For a better understanding of the trap behavior, the required code instructions used to avoid the cause of each trap, are implemented and can be activated by setting the **AVOID\_PROVOCATION** macro to true.

After code compilation and flashing the device, perform the following steps:

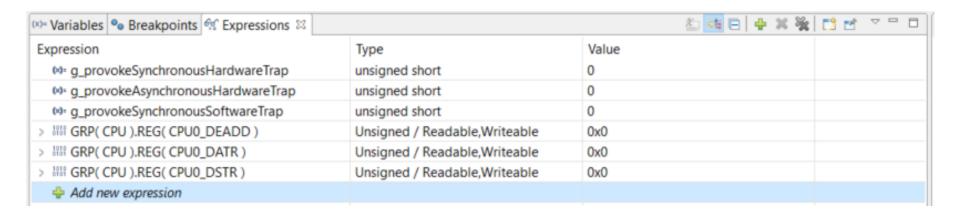

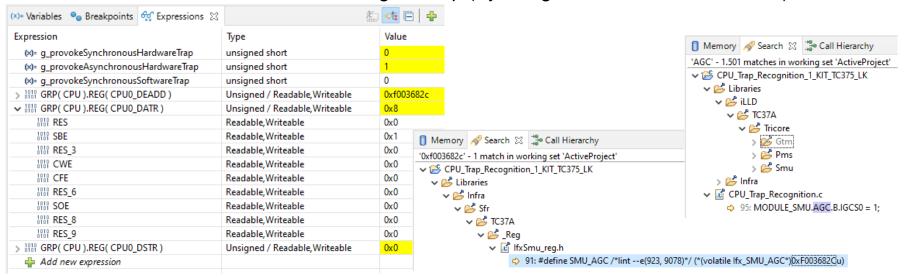

- Add the three variables "g\_provokeSynchronousHardwareTrap", "g\_provokeAsynchronousHardwareTrap" and "g\_provokeSynchronousSoftwareTrap" in the Expressions window of the debugger.

- Add the three registers DEADD, DATR and DSTR in the Expressions window of the debugger.

# infineon

### Run and Test

### 1.1 Synchronous hardware trap

- Provoke the synchronous hardware trap by setting the value of "g\_provokeSynchronousHardwareTrap" in the "Expressions" window to "1".

- Press the "Resume" button to start the program.

- Observe the following information:

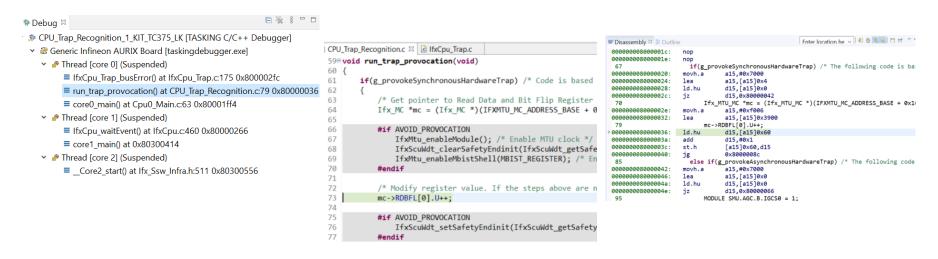

- The debugger stopped in the IfxCpu\_Trap\_busError() function (IfxCpu\_Trap.c).

- The "Variables" window of the debugger displays the "trapWatch" structure and the value of its parameters.

- The trap is provoked by CPU0, it is a trap of class 4, the trap id is 2 and the Return Address (RA) is 0x80000036 (2147483702<sub>10</sub>).

- It is a Data Access Synchronous Error (<u>Trap table</u>, class 4 and tin 2).

### 1.2 Synchronous hardware trap

- Observe the following information:

- The call stack in the "Debug" window displays the function which was called before the trap occurred (in this case the function *run\_trap\_provocation()*, the address displayed behind this function equals the Return Address (RA)).

- By clicking on this function, the debugger jumps to the specific code line in the

CPU\_Trap\_Recognition.c file and to the corresponding assembly line in the "Disassembly" window. The address of the assembly line equals the Return Address (RA).

### 1.3 Synchronous hardware trap

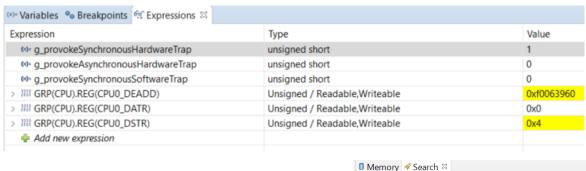

- Observe the following additional information:

- The LBE bit field in the DSTR register is set (Load Bus Error Data load from bus causing error, refer to AURIX™ TC3xx User's Manual).

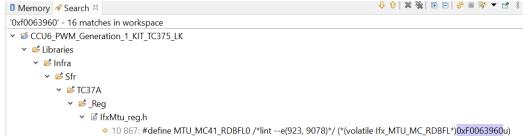

- The **DEADD** register displays the address 0xf0063960, which is the address of the modified register that caused the trap.

- By running a file search (Search -> File) for the address, the search finds the specific RDBFL0 register which equals the modified MBIST DMA register.

### 2.1 Asynchronous hardware trap

- Restart the program by pressing the "Restart" button in the debugger.

- Provoke the asynchronous hardware trap by setting the value of "g\_provokeAsynchronousHardwareTrap" in the "Expressions" window to "1".

- Press the "Resume" button to start the program.

- Observe the following information:

- The debugger stopped in the IfxCpu\_Trap\_busError() function (IfxCpu\_Trap.c).

- The "Variables" window of the debugger displays the "trapWatch" structure and the values of its parameters.

- The trap is provoked by CPU0, it is a trap of class 4, the trap id is 3 and the Return Address (RA) is 0x80000028 ( $2147483688_{10}$ ).

- It is a Data Access Asynchronous Error (<u>Trap table</u>, class 4 and tin 3).

### 2.2 Aynchronous hardware trap

- Observe the following information:

- The call stack in the "Debug" window displays the function which was called before the trap occurred (in this case the function *run\_trap\_provocation()*, the address displayed behind this function equals the Return Address (RA)).

- By clicking on this function, the debugger jumps to the specific code line in the

CPU\_Trap\_Recognition.c file and to the corresponding assembly line in the "Disassembly" window. The address of the assembly line equals the return address.

- Because it is an asynchronous trap, the specific code line is **not** pointing to the line which is causing the trap. It is the code line of the instruction that would have been executed next, if the asynchronous trap had not been triggered.

- Since there is no other instruction within the function run\_trap\_provocation(), it is impossible

to find the line of code by using the Return Address (RA) in this example.

```

** Debug

** CPU_Trap_Recognition_1_KIT_TC375_LK [TASKING C/C++ Debugger]

** ② Generic Infineon AURIX Board [taskingdebugger.exe]

** ② Thread [core 0] (Suspended)

□ IfxCpu_Trap_busError() at IfxCpu_Trap.c:175 0x800002fc

□ run_trap_provocation() at CPU_Trap_Recognition.c:67 0x80000028

□ core0_main() at Cpu0_Main.c:63 0x80001ff4

** ② Thread [core 1] (Suspended)

□ core1_main() at 0x80300416

** ③ Thread [core 2] (Suspended)

□ core1_main() at 0x80300416

```

```

Enter location he V 8 6 5 6 5 6

■ Disassembly

□ Brown Outline

0000000080000020:

a15,#0x7000

a15,[a15]0x4

0000000080000024:

90000000080000028: ld.hu

d15,[a15]0x0

000000008000002c:

jz

d15,0x80000042

Ifx_MTU_MC *mc = (Ifx_MTU_MC *)(IFXMTU_MC_ADDRESS_BASE

000000008000002e:

a15,#0xf006

movh.a

0000000080000032:

a15,[a15]0x3900

79

mc->RDBFL[0].U++;

0000000080000036:

1d.hu

d15,[a15]0x60

000000008000003a:

add

d15,#0x1

000000008000003c:

[a15]0x60,d15

Ifx_MTU_MC *mc = (Ifx_MTU_MC *)(IFXMTU_MC_ADDRESS_BASE

70

0000000080000040:

jg

0x8000008c

else if(g_provokeAsynchronousHardwareTrap) /* The following

0000000080000042:

a15,#0x7000

movh.a

0000000080000046:

a15,[a15]0x0

000000008000004a:

d15,[a15]0x0

```

### 2.3 Asynchronous hardware trap

- Due to the fact that the Return Address (RA) cannot be used, the following information might help to locate the cause of the trap:

- The SBE bit field in the DATR register is set (Store Bus Error Data store to bus causing error, refer to AURIX™ TC3xx User's Manual).

- The **DEADD** register displays the address 0xf003682c, which is the address of the modified register that caused the trap.

- By running a file search (Search -> File) for the address, the search finds the specific

SMU\_AGC register which equals the modified register. The name of the modified register helps to find the code line which is causing the trap (By using another search for "AGC").

### 3.1 Synchronous software trap

- Restart the program by pressing the "Restart" button in the debugger.

- Provoke the synchronous software trap by setting the value of "g\_provokeSynchronousSoftwareTrap" in the "Expressions" window to "1".

- Press the "Resume" button to start the program.

- Observe the following information:

- The debugger stopped in the IfxCpu\_Trap\_assertion() function (IfxCpu\_Trap.c).

- The "Variables" window of the debugger displays the "trapWatch" structure and the value of its parameters.

- The trap is provoked by CPU0, it is a trap of class 5, the trap id is 1 and the Return Address (RA) is 0x80000086 (2147483782<sub>10</sub>).

- It is an Arithmetic Overflow Error (<u>Trap table</u>, class 5 and tin 1).

### 3.2 Synchronous software trap

- Observe the following information:

- The call stack in the "Debug" window displays the function which was called before the trap occurred (in this case the function *run\_trap\_provocation()*, the address displayed behind this function equals the Return Address (RA)).

- By clicking on this function, the debugger jumps to the specific code line in the

CPU\_Trap\_Recognition.c file and to the corresponding assembly line in the "Disassembly" window. The address of the assembly line equals the Return Address (RA).

```

♦ Debug

□

CPU_Trap_Recognition_1_KIT_TC375_LK [TASKING C/C++ Debugger]

Generic Infineon AURIX Board [taskingdebugger.exe]

IfxScuWdt_setSafetyEndinit(IfxScuWdt_getSafetyWatchdogP

P Thread [core 0] (Suspended)

100

/* After configuration, set a temporary lock of the SMU

■ IfxCpu Trap assertion() at IfxCpu Trap.c:186 0x800002b8

101

IfxSmu_lock(&MODULE_SMU);

102

= run_trap_provocation() at CPU_Trap_Recognition.c:121 0x80000086

103

core0 main() at Cpu0 Main.c:63 0x80001ff4

Enter loca

Disassembly Size Outline

104

else if(g_provokeSynchronousSoftwareTrap)

105

P Thread [core 1] (Suspended)

d0.#0xfe04

0000000080000074:

106

Ifx CPU PSW psw;

/* Variable of the type PSW (Pr

■ IfxCpu waitEvent() at IfxCpu.c:460 0x80000266

110

psw.B.USB = 0x40;

/* Set the

107

0000000080000078:

mov

d15,#0x40

108

core1_main() at 0x80300414

/* Get the content of the Program Status Word register

109

psw.U = __mfcr(CPU_PSW);

000000008000007a:

d15,d0,d15,#0x18,#0x8

P Thread (core 2) (Suspended)

110

psw. B. USB = 0x40;

/* Set the overflow bit in the

_mtcr(CPU_PSW,psw.U); /* Write th

__Core2_start() at lfx_Ssw_Infra.h:511 0x80300556

000000008000007e:

mtcr

#0xfe04.d15

#if AVOID_PROVOCATION

0000000080000082:

113

isync

psw.B.USB = 0x0;

/* Reset the overflow bit in th

114

_asm("trapv");

121

115

00000000080000086:

trapv

__mtcr(CPU_PSW,psw.U); /* Write the modified register

116

109

= mfcr(CPU PSW);

117

0x8000008c

000000008000008a:

1189

/* TRAPV instruction (trap on overflow) call, assembly

119

* If the overflow bit is set, an Arithmetic Overflow 7

120

000000008000008c:

121

asm("trapv");

Ifx__imaskldmst(event, 1, __mfcr(CPU_CO

000000008000008e:

mfcr

d15,#0xfe1c

123

else

d0/d1,#0x1,d15,#0x1

1dmst

[a4]0x0,d0/d1

```

# References

- > AURIX™ Development Studio is available online:

- https://www.infineon.com/aurixdevelopmentstudio

- Use the "Import…" function to get access to more code examples.

- More code examples can be found on the GIT repository:

- https://github.com/Infineon/AURIX code examples

- For additional trainings, visit our webpage:

- https://www.infineon.com/aurix-expert-training

- For questions and support, use the AURIX™ Forum:

- https://www.infineonforums.com/forums/13-Aurix-Forum

### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2021-03 Published by Infineon Technologies AG 81726 Munich, Germany

© 2021 Infineon Technologies AG. All Rights Reserved.

Do you have a question about this document?

Email: erratum@infineon.com

Document reference CPU\_Trap\_Recognition\_1 \_KIT\_TC375\_LK

### **IMPORTANT NOTICE**

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on the product, technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies office (<a href="www.infineon.com">www.infineon.com</a>).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.